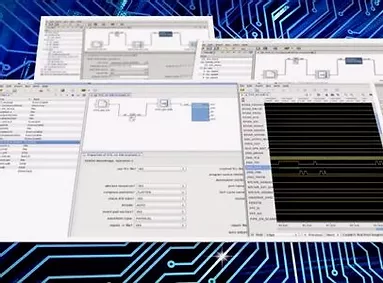

STILDirector

STILDirectorとは

国際的な標準テスト記述言語STILに対応した設計・テスト環境(デザインキット)を構築するツールでです

STILでテスト開発TAT短縮

従来のテスト開発では、テスト設計、設計検証、テストプログラム作成、テスト、故障解析の各工程において、テストデータの記述方法が異なり、工程間のテストデータ、テスト情報の変換や、言語や記述フォーマットの習得が必要でした。変換ミスや、後戻りがあるとTATが増大します。また、テスト記述言語によっては、タイミングやパターン記述に制約があったり、手間がかかったりしています。

そこで、STILをベースとしてテスト環境を構築することによって、全てのテストデータをSTILで取り扱うことによって、各工程でのデータ変換作業が無くなります。 ATPGテスト生成ツールやシミュレータから生成される、また、IPベンダから供給されるSTIL記述のテストベクタを利用できるため、効率の良いテストベクタ作成、テスト設計が可能となりテスト開発期間の短縮、テストコストの削減を図ることができます。

オープンシステムとして既設システムにプラグイン

また、オープンシステムとして提供していますので、お客様の環境へも簡単にプラグインでき、アクセスインターフェースを用いて様々な環境に合わせたカスタマイズが可能なシステムとなっています。 STILDirectorにより、早く、安く、確実にお客様のSTILベースのテスト環境を構築できます。

STILDirectorの構成

STILパーサー

テストベクタ生成ツールで作成されたSTIL、ファンクションベクタ、IPテストベクタなどSTILで記述されたファイルをSTILDirectorのSTILデータベースに読み込みます。STILデータの言語仕様上の違反をチェックします。

STILジェネレータ

シミュレータ出力結果などからSTILデータベースに読み込まれたデータからSTILファイルを生成します。

シミュレータインタフェイス

STILデータベースからシミュレーション用入力ファイルを生成します。テスタルールチェックを施したベクタデータを入力として、再度シミュレーションを実行することができます。また、シミュレーション結果をサイクルに分割(サイクライズ)してSTILデータベースに取り込みます。さらに、シミュレーション結果を元にDC測定アドレスを抽出します。

テスタルールチェック

テスタで実行できるか事前にチェックすることができます。

アクセスインタフェイス

STILデータベースからデータを読み出したり、書き込んだりするアプリケーション・プログラミング・インターフェイスを使って、既設環境に合わせたユーザアプリケーションプログラムを作成することができます。

テスタインタフェイス

テスタ用テストデータの生成が可能です。

故障シミュレータインタフェイス

故障シミュレータ用入力ファイルを生成します。

STILDirectorの特徴

STILデータとのインタフェイス

- STILデータの読み込み及び出力ができます

- STILの言語仕様上の違反をチェックできます

読み込み可能なATPGツールが出力するSTIL

- Synopsys TetraMAX

- Mentor FastScan

- Cadence TestBench/Encounter

シミュレータとのインタフェイス

- 各種シミュレータの入力を生成できます

- 各種シミュレータの結果ファイルを入力できます

- シミュレーション結果を解析することができます

- シミュレーション結果から期待値を自動抽出しSTILファイルを作成できます

- DC測定アドレスを自動的に抽出します

サポートするシミュレータ

- Verilog-XL

- NC-Verilog

- NC-VHDL

- NC-SIM

- ModelSim

- VCS

テスタとのインターフェイス

- テスタで使用できるパターン記述であるかを、テスタ実行前にチェックできます

- シミュレーション結果をサイクライズできます

既設システムとのインタフェイス

利用者の環境へプラグインできるオープンシステム構成となっています データベースのアクセスインタフェイスと組み合わせて、カスタマイズできます

サポートするプラットフォーム

- Linux / Intel PC

その他

STILDirectorはエンジニアリングワークステーション上で動作します