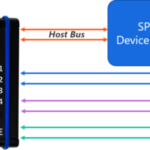

パラレル、シングルエンド、超高速

![]() 半導体業界で最も急速に成長している分野であるメモリ技術は、密度、効率、転送速度が急速に向上し続けています。最新世代のDDR(ダブルデータレート)メモリ・インターフェースを構築する場合、開発者は、設計検証とインターフェースの特性評価の両方の段階で、これまでにない課題に直面します。一方で、DDRインターフェースはシングルエンドであり、1つのメモリ・デバイスに対して大量の信号トレースが必要となります。また、DDR4やDDR5などの最新規格では、非常に正確な測定セットアップが必要となり、レシーバのストレス要件も含まれます。

半導体業界で最も急速に成長している分野であるメモリ技術は、密度、効率、転送速度が急速に向上し続けています。最新世代のDDR(ダブルデータレート)メモリ・インターフェースを構築する場合、開発者は、設計検証とインターフェースの特性評価の両方の段階で、これまでにない課題に直面します。一方で、DDRインターフェースはシングルエンドであり、1つのメモリ・デバイスに対して大量の信号トレースが必要となります。また、DDR4やDDR5などの最新規格では、非常に正確な測定セットアップが必要となり、レシーバのストレス要件も含まれます。

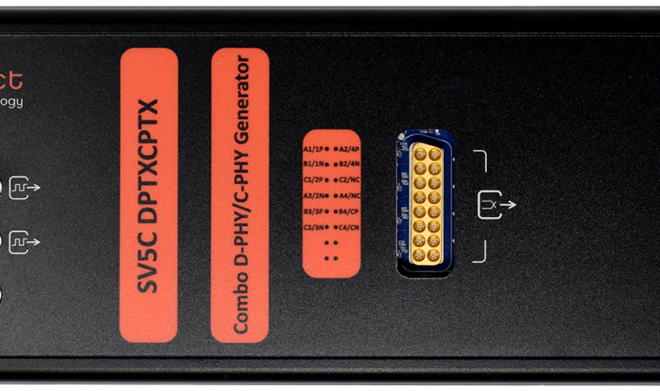

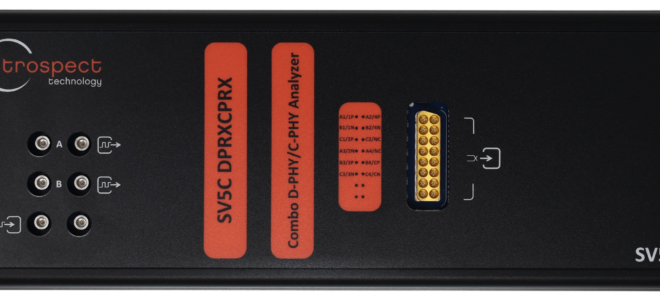

Introspect Technology社の高度に並列化されたパターン・ジェネレータおよびシグナル・アナライザ・ソリューションは、DDR4およびDDR5のインターフェース・テストに最適です。当社のソリューションには、DDRアプリケーション用に特別に調整されたプロトコル機能と物理層機能の幅広いホストが含まれています。さらに、これらの機能はすべて、CPUメーカー、インターフェース・メーカー、DRAMメーカー、システム・インテグレーターにとって非常に魅力的な価格で提供されています。

業界の課題

- 高いデータレート

- チャンネル数が多い

- 厳しいスキュー要求

- シングルエンド

- 決定的なパターンのタイミング

機能

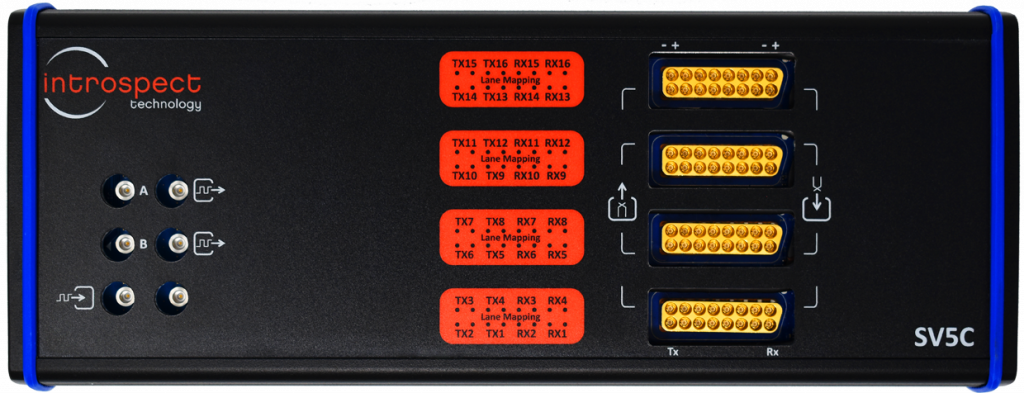

- DDR関連のテスターでは最大12.5 Gbp

- 構成されたセットアップで最大112チャネル

- 決定論的で高精度なスキュー制御

- パターン・タイムライン・テクノロジー

DDR4/DDR5アプリケーションにおけるSV5Cパターンのタイムラインを理解する

このチュートリアルでは、Introspect Technology社のパターン・タイムライン・ツールについて学びます。このツールは、任意のプロトコル・トラフィックを数分で生成するために使用できる、強力なコマンドおよびパターン・シーケンサーです。このチュートリアルでは、SV5Cでの基本的なパターン生成のコンセプトを説明した後、パターン・タイムライン・ツールを使って洗練されたDDR5のタイミング・ダイアグラムの作成に進みます。 このチュートリアルは、DDR4/DDR5アプリケーションに携わる設計エンジニア、システム検証エンジニア、テスト・エンジニアで、ATEテストやキャラクタリゼーションに焦点を当てている方に役立ちます。

DDR5 DIMMのファンクション・テストは難しくないが、複雑である

PV2 ユニバーサル・アクティブ・プローブ

SV5D

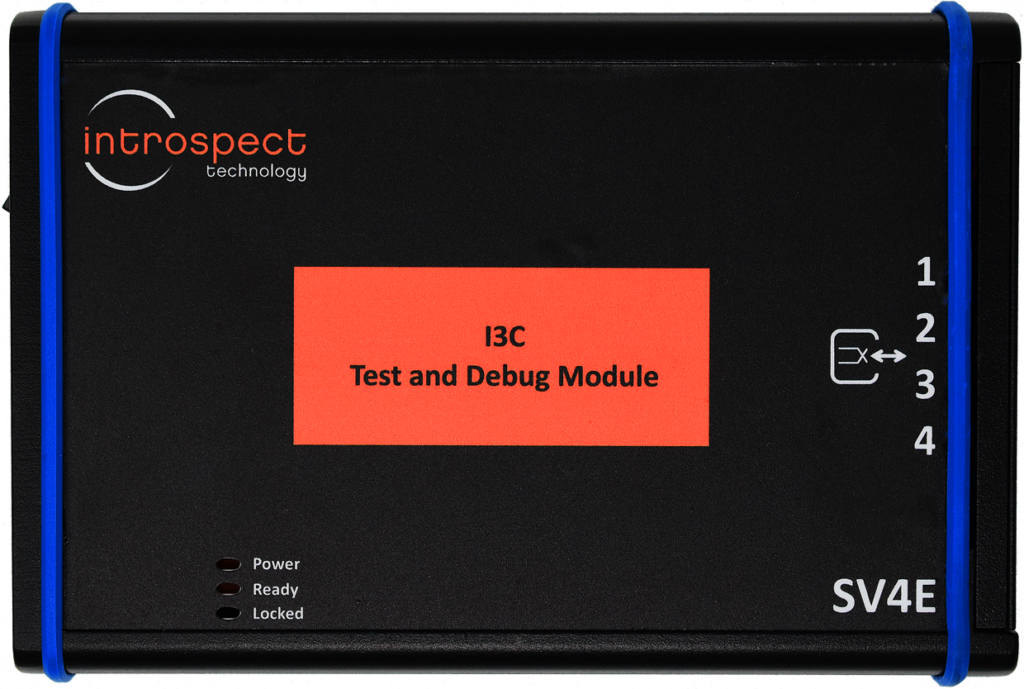

SV4E-I3C

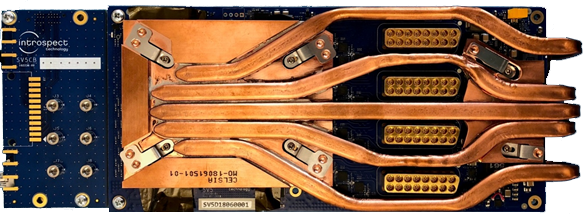

SV5C-12

PV1 ユニバーサル・アクティブ・プローブ

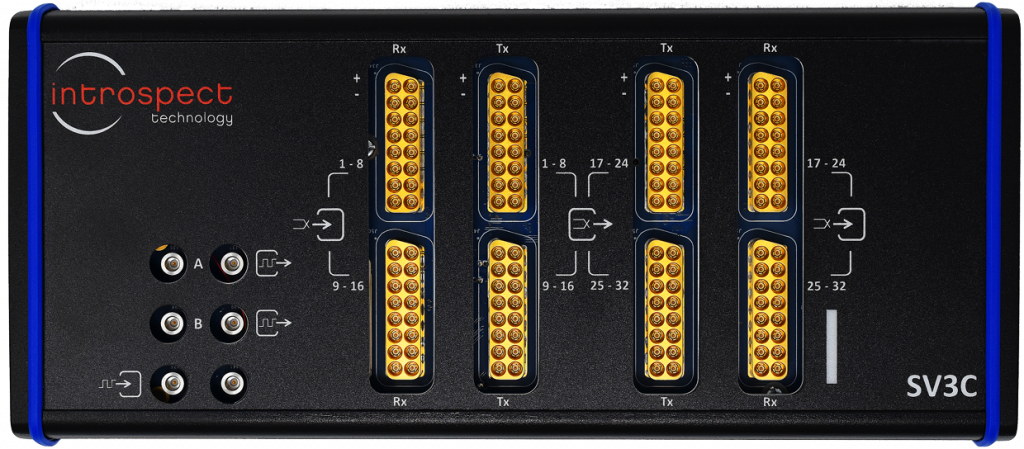

SV3C パーソナライズドSerDesテスター