はじめに

DDR(Double Data Rate)技術は、サーバーやデータセンターだけでなく、パソコンやゲーム機などにも広く使われているメモリーチップ技術です。高いメモリ密度とメモリ容量、そして高速な転送速度を特徴とし、データセンターの高性能コンピューターやAIプロセッサー、エッジコンピューターの導入に欠かせない技術となっています。この技術は、JEDECのDDR5規格という形で第5世代に入りましたが、メモリモジュールメーカーやサーバーメーカー、システムインテグレーターにとっては、独自の開発課題となっています。その主な理由は、DDR5では、リンク・イコライゼーションや高度なトレーニング・アルゴリズムなど、超高速動作を可能にするいくつかの新機能が導入されているからです。

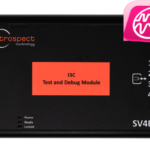

この記事では、DDR5規格のメモリモジュールをテストする上での課題を紹介します。ここでは、DDR5規格のメモリ・モジュールをテストする際の課題を紹介します。特に、機能テストの側面に焦点を当てています。機能テストを実現するためには、データレートの増加、プロトコルの複雑化、高密度化に関連するいくつかのハードルを克服する必要があることが示されます。続いて、SV5Cパーソナライズド・SerDesテスト・システムで構成されるIntrospect Technology社のATE-on-Benchソリューションについて説明し、DDR5ステート・マシンの内部動作の可視性と制御を提供するコンテキスト内で、完全なメモリ・コントローラをエミュレートするためにどのように使用されるかを説明します。SV5C DIMMテスト・スイートでは、Pythonプログラミングにより、仮想メモリ・コントローラを実装し、カスタマイズすることができます。次に、デバイスの初期化ステップとトレーニング・アルゴリズムがどのようにシーケンスされ、機能的な読み取り/書き込み操作が実行されるのか、その例を説明します。

機能テストの課題

DDR5規格によってもたらされた新たな課題を以下にまとめました。

高速化

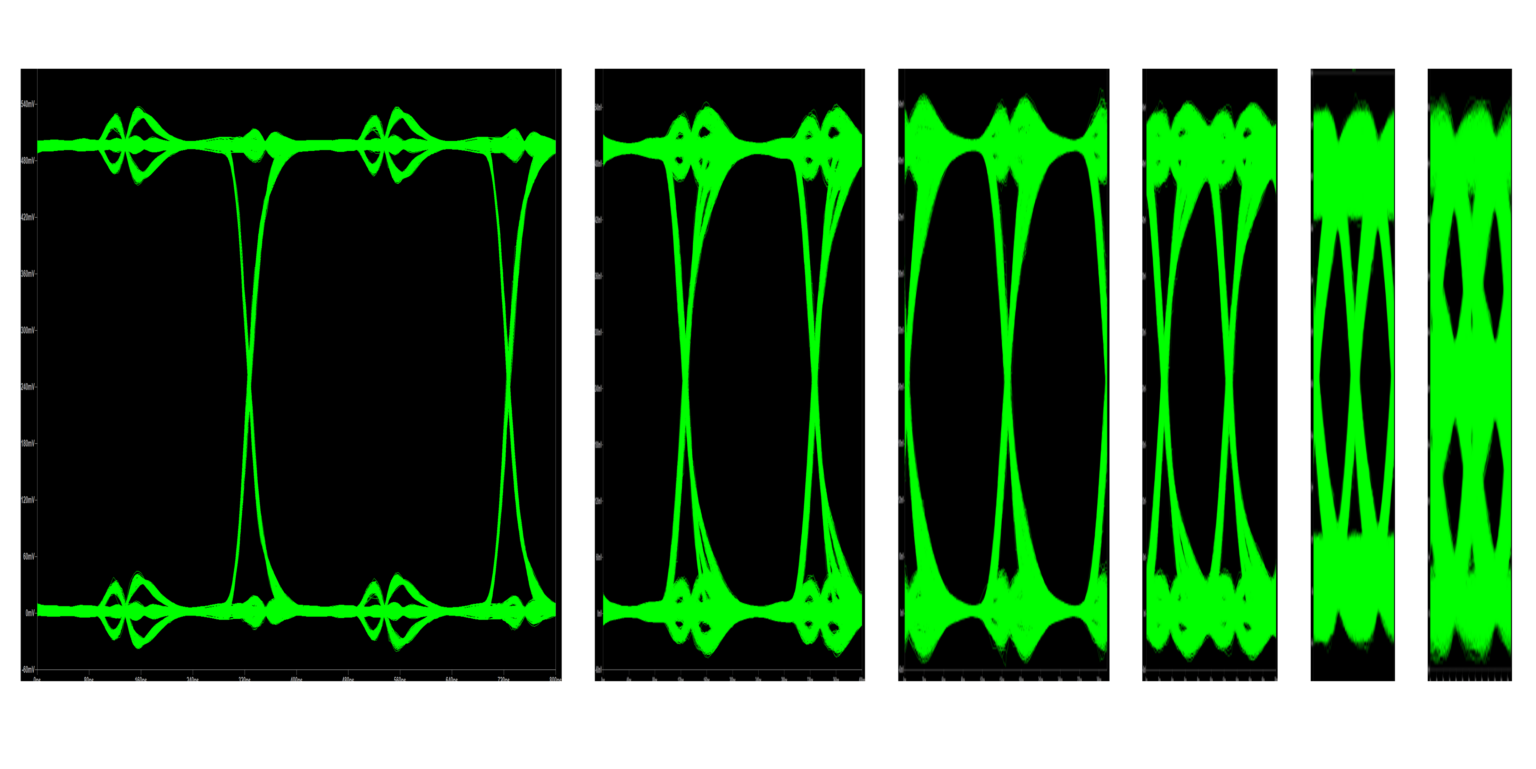

従来のDDRの実装とは異なり、メモリ・コントローラでセットアップ時間とホールド時間を定義するだけで、メモリのリード/ライト・オペレーションにエラーが発生しないことを期待することはもはや不可能です。その代わりに、DDR5では、ビット・エラー・レートやアイダイアグラムの統計など、統計的なパフォーマンス・パラメーターが定義されています。さらに、DDR5のリンクは、プリント基板(PCB)のチャネル上で動作するため、アイダイアグラムが閉じてしまい、高度なトレーニング・アルゴリズムが必要になります。

プロトコルの複雑化

上記のトレーニングアルゴリズムは、メモリコントローラとそれに接続されたメモリモジュール間の適切なハンドシェイクを保証するための新しいプロトコル要件によって実装されています。簡単に言えば、メモリモジュールの電源を入れただけでは、読み書きのトランザクションを実行することはできないということです。むしろ、設計者は、出荷するモジュールにプロトコル適合性を考慮しなければなりません。

このようにプロトコルが複雑化しているため、DIMMメーカーやメモリコントローラーにとって、機能テストを行うことができるサードパーティ製のテスト機器を利用することが非常に重要です。また、DDR5のステートマシンで使用されているトレーニングアルゴリズムを変更・カスタマイズするのに十分な粒度を提供することも重要です。

より高いメモリ密度

当然のことながら、DDR5メモリ・モジュールはより高いメモリ容量をサポートしているため、テストは前世代よりも徹底的に行う必要があります。つまり、テスト対象のメモリを完全にスキャンするためには、より多くの読み取り/書き込みトランザクションが必要になります。機能テスト・システムには、このようなメモリ・スキャンを、アルゴリズムまたはテスト・パターン・データのバンクを使って実行できることが求められます。

ハードウェア接続図

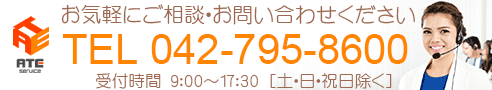

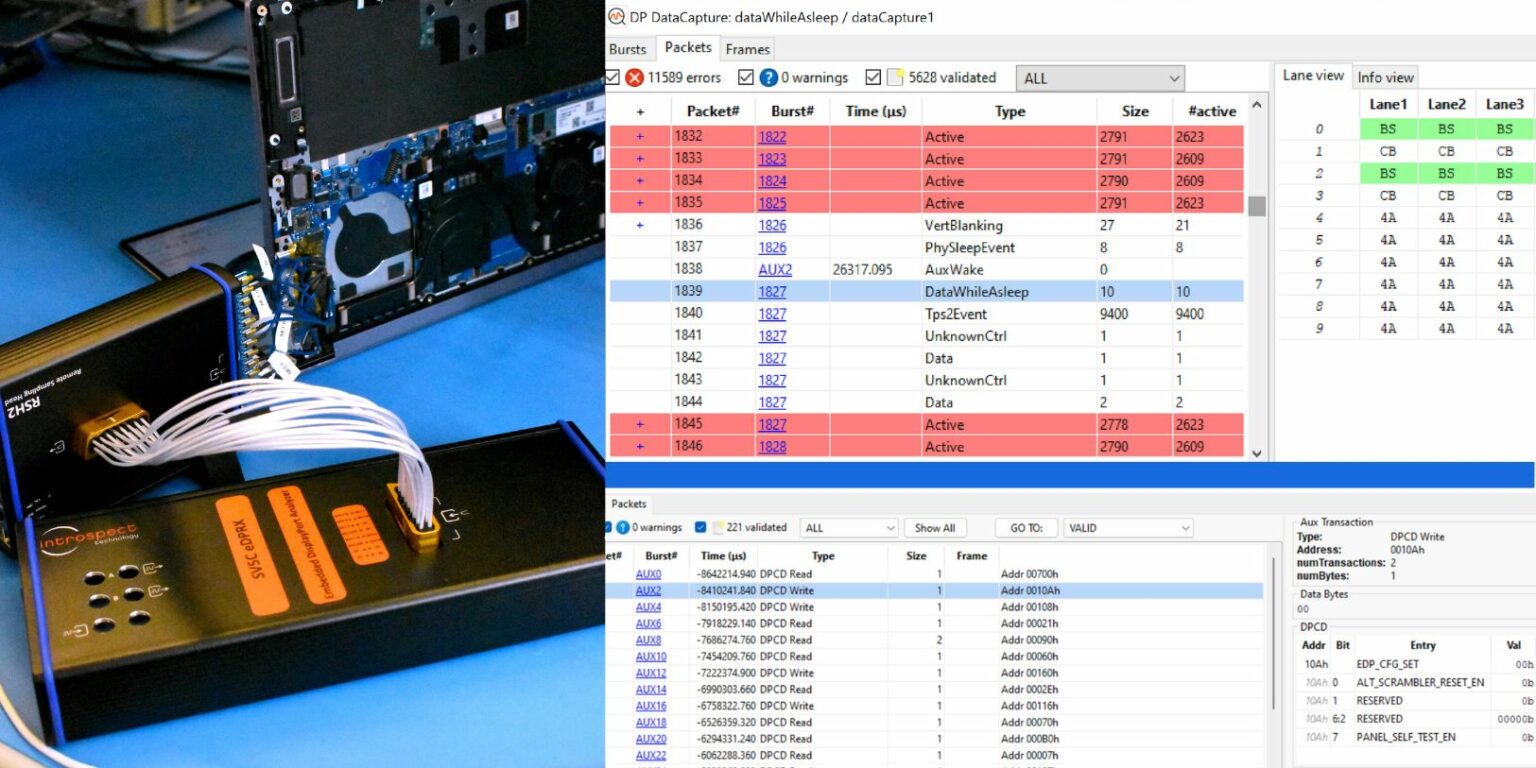

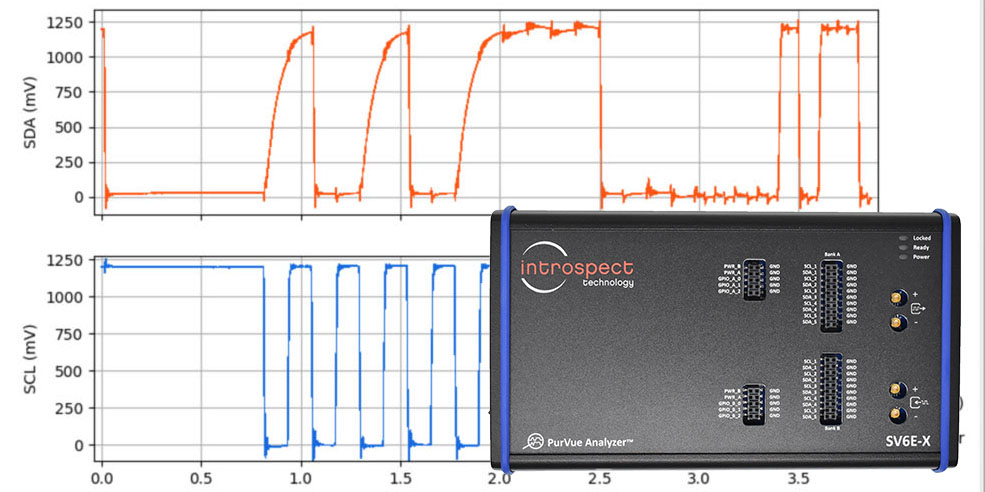

図 1 は、被試験メモリ・モジュールと SV5C ATE-on-Bench システムのハードウェア接続の概略を示しています。このように、複数の SV5C モジュールを組み合わせて、ワイドバス・アプリケーションを構築することができます。さらに、テストシステムにはBDK(Bidirectional Communications Kit)が搭載されており、DIMMのデータ信号とストローブ信号に使用されます。

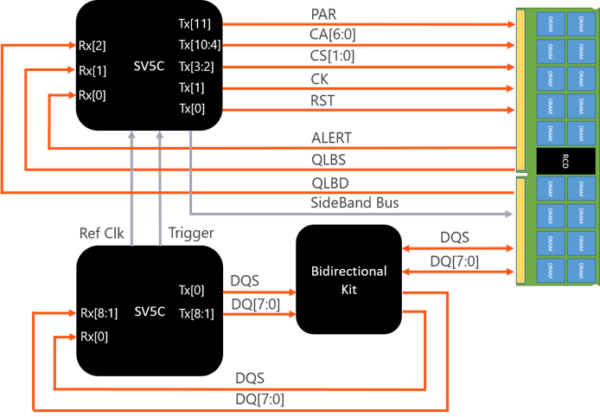

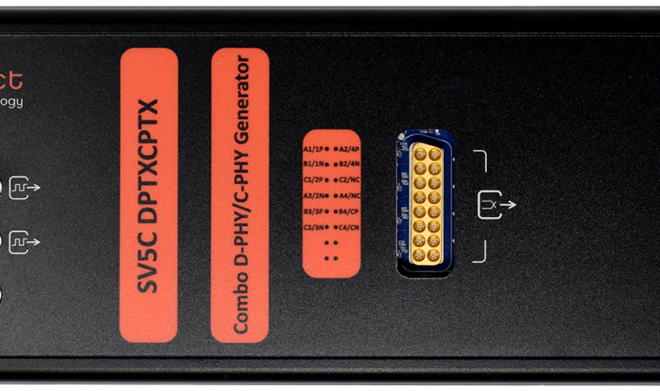

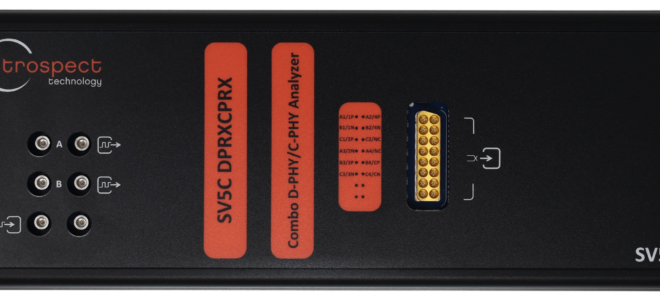

図2は、そのセットアップの写真です。このように、SV5Cシステムは、被試験品であるDIMMのすぐそばに設置できる非常にコンパクトなソリューションです。この図では、JEDECで定義されたCTC2ボード上にテスト対象のDIMMが置かれており、DIMM上のすべての信号に容易にアクセスできるようになっています。

Introspect社のTest Suiteのコンセプト

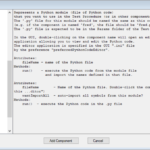

SV5C システムの Test Suite ソフトウェア・インターフェイスには、DDR5 のステート・ダイアグラムの各ステー トを表す Python 関数や、テスト・システムの初期化やプログラミングに関連するステートが用意されています。以下では、このインターフェースを使用したメモリ・コントローラの構築方法と、トレーニングから機能的な読み書きのトランザクションに至るまでの遷移の例を説明します。

DDR5の状態図と仮想メモリ・コントローラ

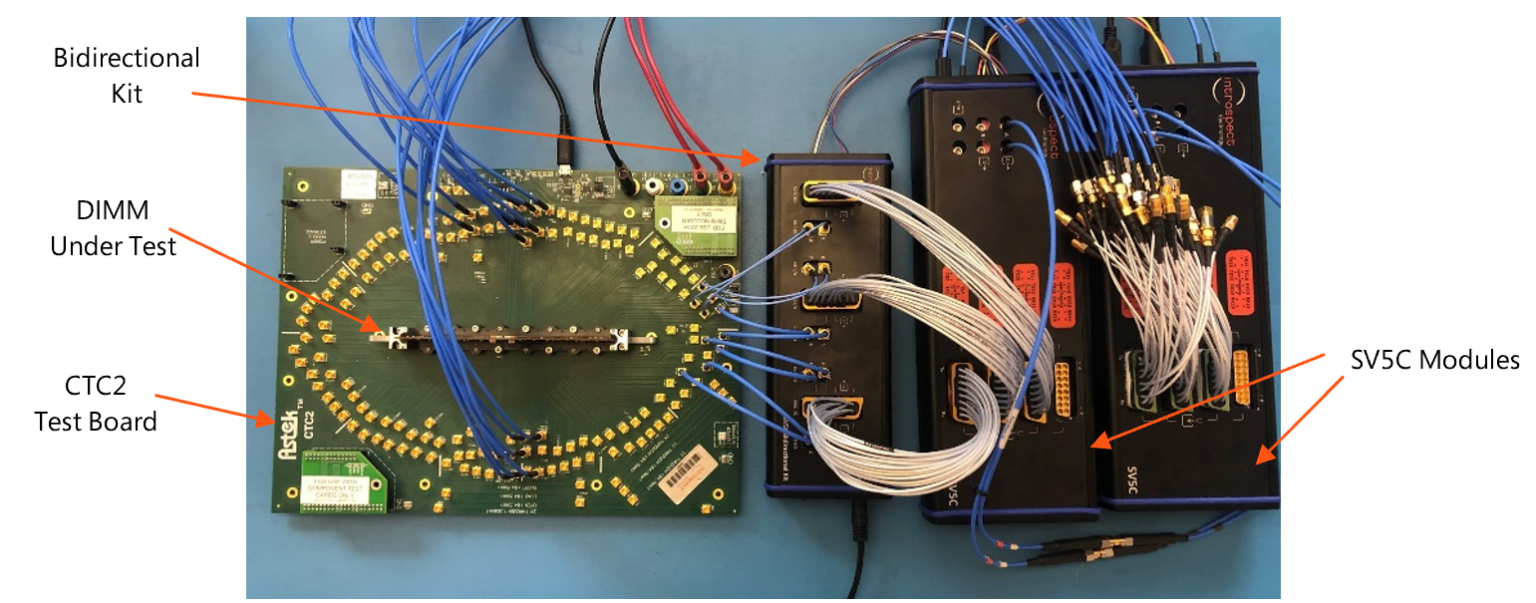

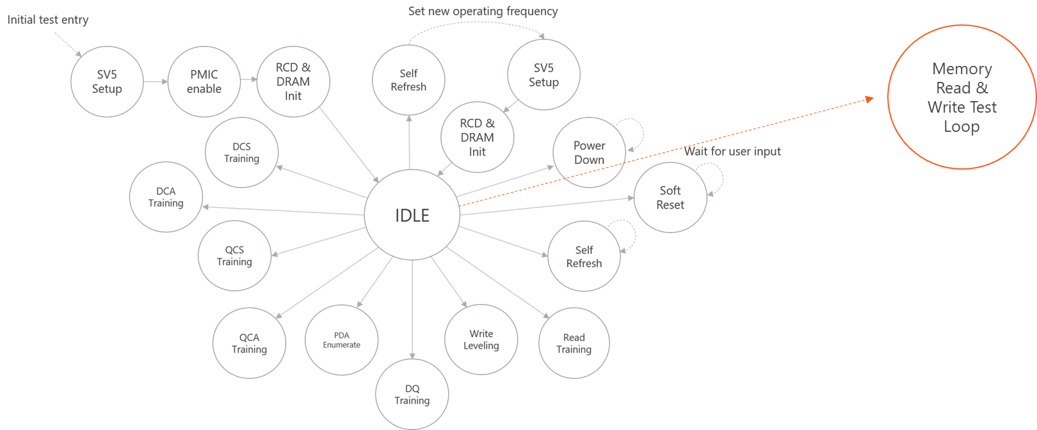

図3は、SV5C DIMM Test Suiteの基本的な状態図です。この図は、一般的なメモリ・コントローラの状態図を非常によく反映していることがわかります。これが、本ホワイトペーパーで仮想メモリ・コントローラと呼ばれている理由です。

この図には、DDR5の状態だけでなく、SV5Cテスト・システムに関連する状態も示されています。例えば、左上の状態では、SV5Cの初期化やデータレートのプログラムなどを行います。同様に、右上の状態では、DDR5 の状態図を崩すことなく、SV5C をプログラムして動作データ・レートを変更することができます。テスト・スイート内のすべてのアクションはアイドル状態に移行できるため、実際のメモリ・コントローラと同様に、バス上のDeselect(DES)コマンドを使用して、DDR5リンクを常にアクティブに保つことができます。

トレーニング状態と機能状態の移行

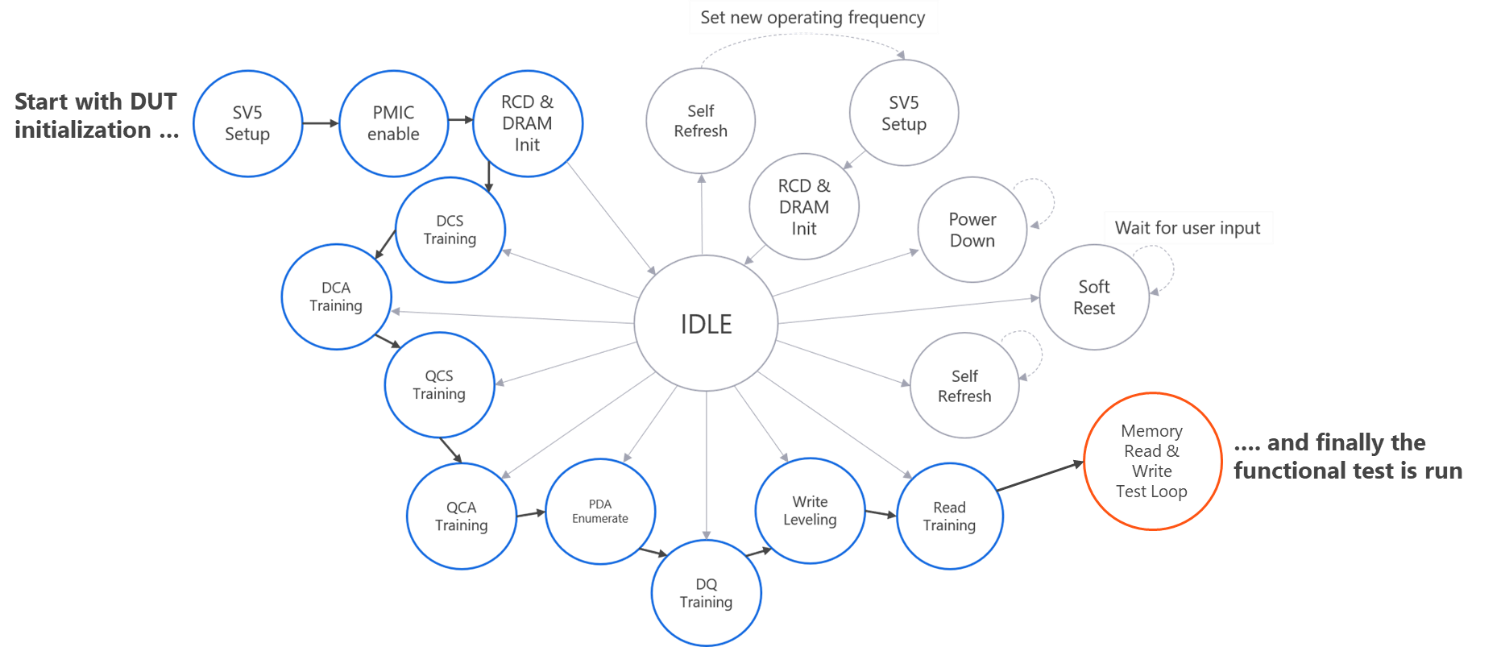

図4は、テスト対象のDIMMが、メモリの読み書きテストループを実行するように移行する方法を示しています。具体的には、Test Suite に 1 つの Python 関数を追加し、この Python 関数にすべてのメモリ テスト コードを含めることができます。重要なのは、この関数は、メモリコントローラの設計全体を知らなくても、図3のオリジナルの状態図に取り付けることができることです。

事前に構築された基本的なテストケースの上にテストを追加できることは、SV5CテストシステムのDIMMテストにおける最も重要な機能の一つです。これにより、ユーザーは、トレーニングやライトレベリング、エニュメレーションなど、DDR5の状態図の詳細を気にすることなく、メモリへの書き込みや読み出しといった作業に集中することができます。

初期化からメモリアクセスまでの流れの例

最後に、デバイスの初期化からメモリの読み書きを実行するまでの流れを図5に示します。見ての通り、多くの複雑なステップが必要です。初心者の方や、メモリ・アレイ自体に興味のある方は、これらの手順を SV5C のテスト・システムが自動的に実行することができます。また、SV5Cは過去に取得した学習データを保存することができるので、さらに実行が簡単になります。

おわりに

このホワイトペーパーでは、DDR5 規格のメモリモジュールをテストする際の課題を紹介しました。機能テストに焦点を当て、DDR5 DIMM の機能テストにおいて、この新しい高性能な規格に関連する、明らかに複雑な問題のいくつかをどのように解決できるかを説明しました。メモリ・コントローラのステート・ダイアグラムのトレーニング・シーケンスは非常に複雑ですが、SV5C ATE-on-Benchソリューションは、テスト対象のDIMMを初期化から、メモリの読み書きが可能な状態まで自動的にシーケンスできることを示しました。