パーソナライズドSerDesテスター

メリット

- 任意のレートでのプログラミング

- 任意のパターン生成(PRBS,クロック・パターンを含む)

- BERT、アイダイアグラム、アナログ波形の測定機能

- 全レーンのジッター・インジェクションおよびノイズ・インジェクションを完全に合成して統合

- 全レーンのジッター・テストを完全自動化

- レーンごとのTX振幅、プリエンファシス、およびファイン・スキュー制御

- レーンごとのRXクロックリカバリおよびイコライゼーション

- 柔軟なループバックのサポート

- 直感的な操作が可能なPython言語をベースとした最新のプログラミング環境

特長

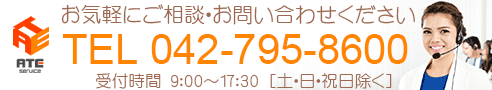

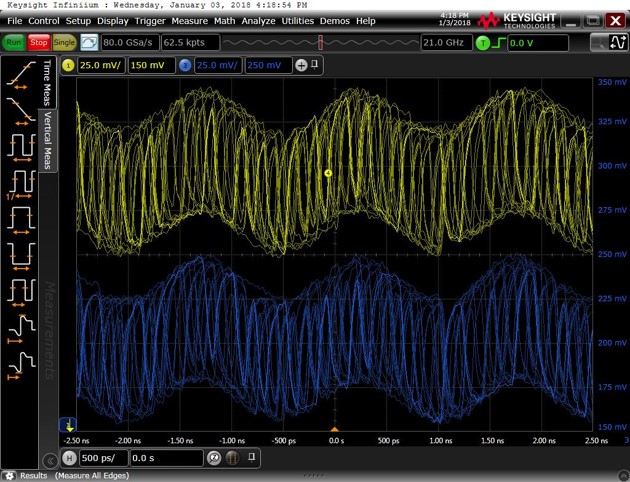

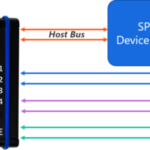

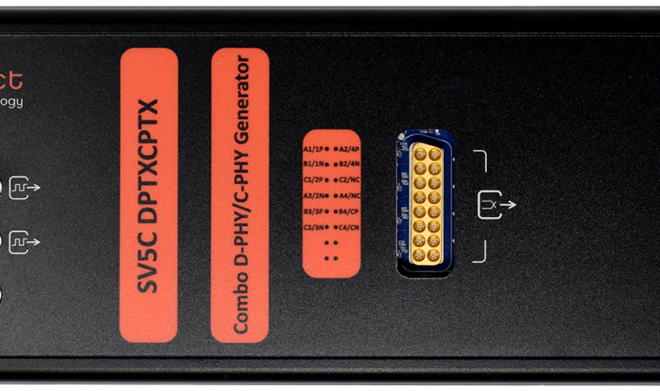

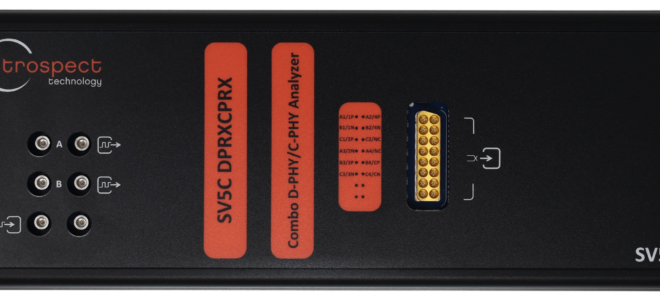

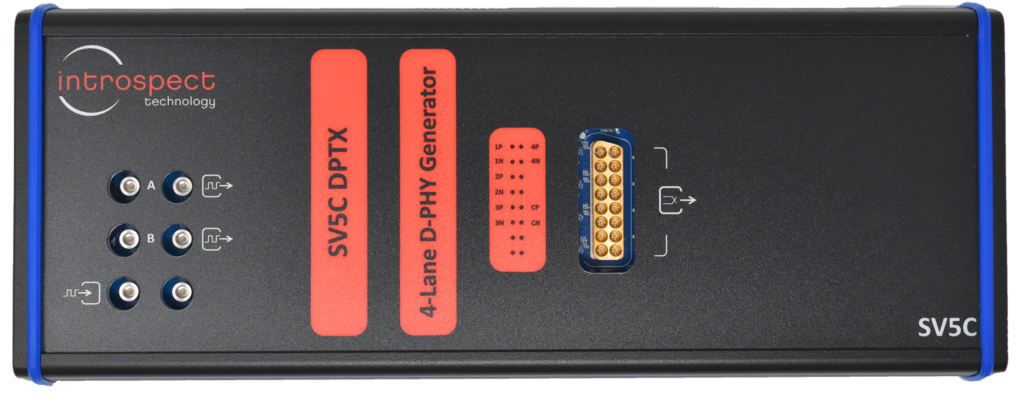

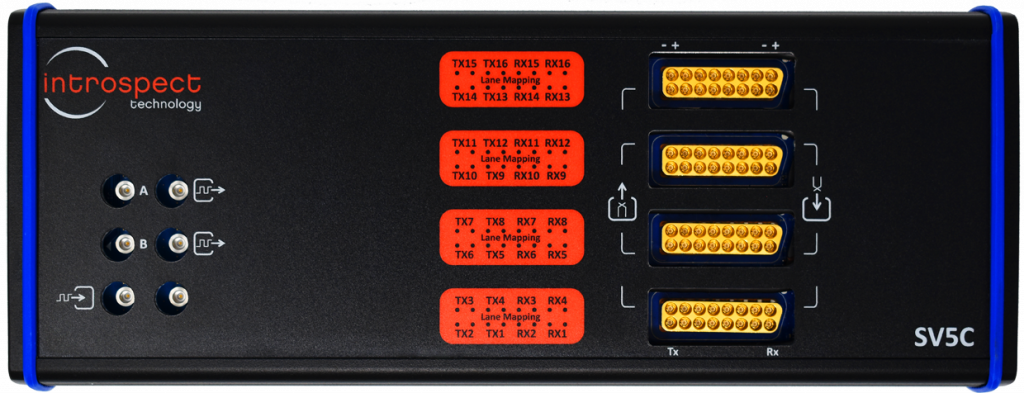

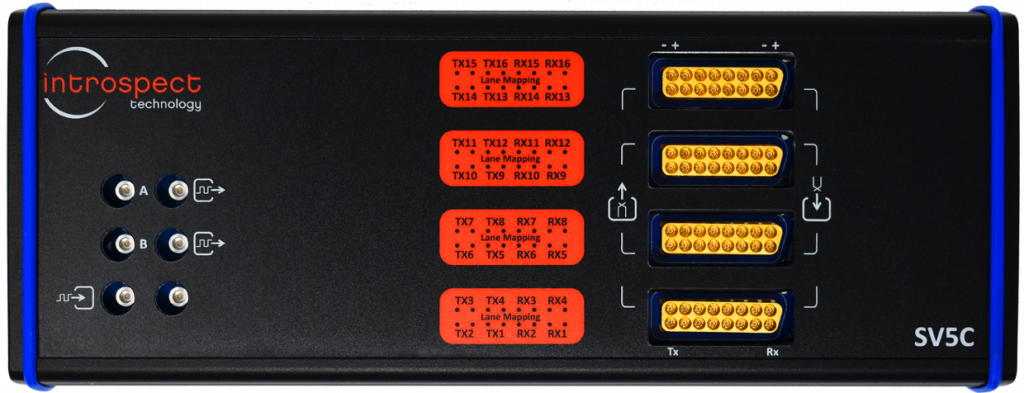

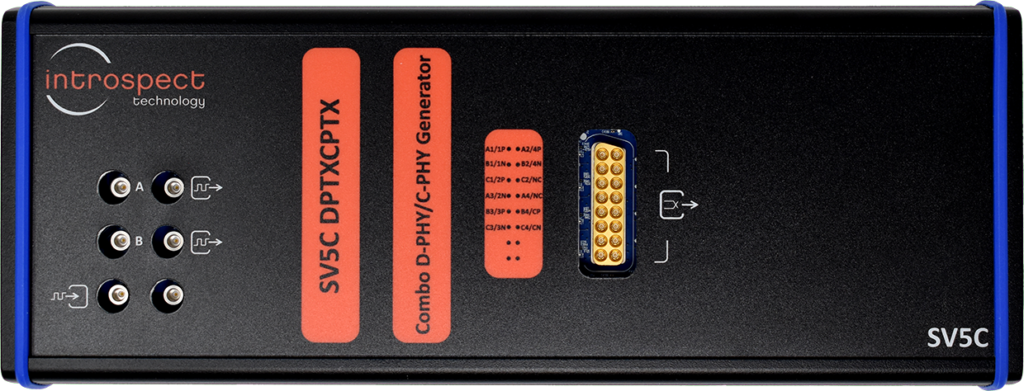

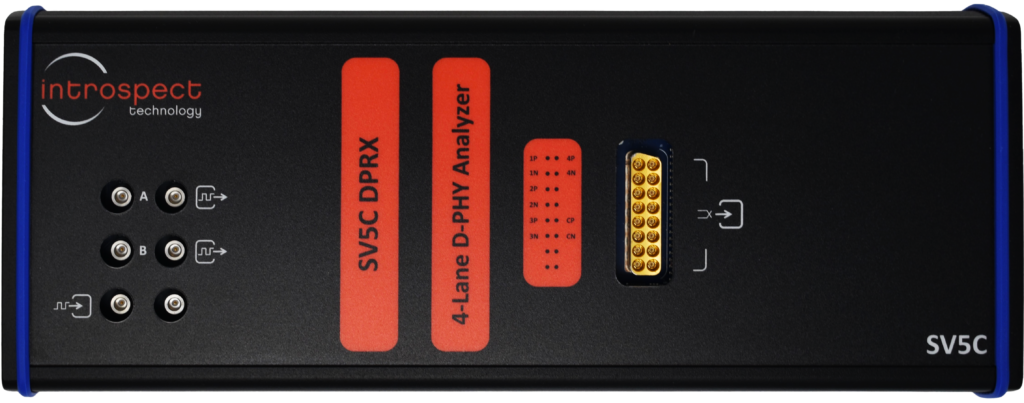

SV5CパーソナライズドSerDesテスターは、高機能・高集積のパラレルBERTソリューションであり、テストカバレッジを向上させ、マルチチャネル・インターフェース・リンクの性能を深く理解することができます。SV5Cは、16レーン、最大12.5Gbpsのデータレートで同時にトラフィックを生成して測定することにより、世界クラスのシグナルインテグリティとチャネル間のアイソレーションを提供しながら、現実的なシステムのような条件でSerDesリンクを評価するユニークな機会を提供します。

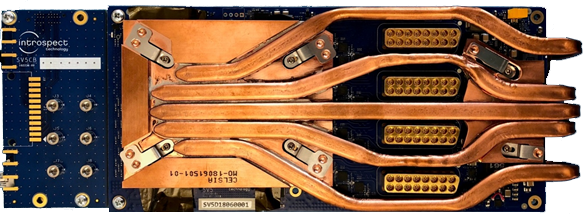

SV5Cは、PCI Express Gen4や今後予定されている様々なMIPI規格などのパラレル・インターフェースの検証ニーズに対応するためにゼロから設計されており、デジタル信号処理、アナログ処理、マイクロ波信号伝搬、データ解析、熱設計などの分野における革新的な技術が盛り込まれています。

Introspect ESPソフトウェアと一緒に使用することで、SV5Cは、テスト・オートメーション・スイート、デバイス電源、デバイス・ハンドラ、デバイス・コントロール・プローブで構成される完全な量産型キャラクタライズ・ステーションの不可欠な要素となります。

DDR4/DDR5アプリケーションにおけるSV5Cパターンのタイムラインを理解する

このチュートリアルでは、Introspect Technology社のパターン・タイムライン・ツールについて学びます。このツールは、任意のプロトコル・トラフィックを数分で生成するために使用できる、強力なコマンドおよびパターン・シーケンサーです。このチュートリアルでは、SV5Cでの基本的なパターン生成のコンセプトを説明した後、パターン・タイムライン・ツールを使って洗練されたDDR5のタイミング・ダイアグラムの作成に進みます。 このチュートリアルは、DDR4/DDR5アプリケーションに携わる設計エンジニア、システム検証エンジニア、テスト・エンジニアで、ATEテストやキャラクタリゼーションに焦点を当てている方に役立ちます。