DDR、LPDDR、GDDR のいずれであっても、メモリ PHY とメモリコントローラをテストするというトピックは、最近、業界で大きな注目を集めている。その理由は、JEDEC の仕様が通常メモリ・デバイスの仕様にのみ焦点を当てているのに対して、メモリ・システム全体の性能は、基本的にコントローラとコントローラのメモリ PHY がいかに効果的に機能するかにかかっているからである。これは、最大28Gbpsの転送速度に達し始めている最新世代の実装に特に当てはまる。このような転送速度では、メモリコントローラとメモリ PHY のメーカは、SerDes スタイルの測定要求と格闘している。

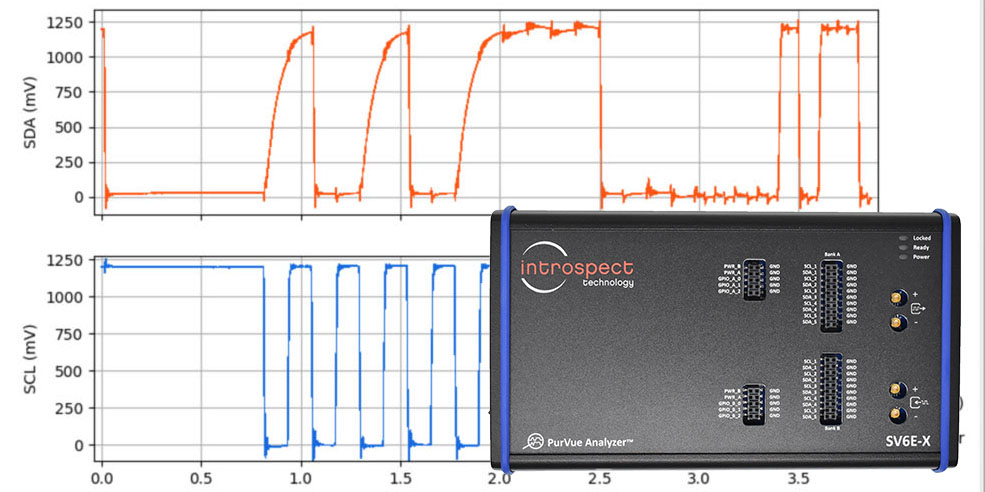

Introspect Technologyは、DDR、LPDDR、GDDRテスト用の専用ツールを開発し、上記の業界の難問を解決するのに理想的です!Introspectの課題と対応するソリューションの詳細については、続きをお読みください。

メモリPHYアーキテクチャ

一般的なメモリ PHY アーキテクチャを図 1 に示す。上述したように、異なるメモリインタフェース(DDR, LPDDR, GDDR)間で、実装の具体的な詳細は若干異なるが、図 1 に示すような共通項がある。すなわち

- メモリコントローラ/メモリ PHY は、ソース同期コマンドとアドレスバスを持っている。

- メモリコントローラ/メモリ PHY は双方向のリード/ライトバスを持つ。

- メモリコントローラ/メモリ PHY は、クロック逓倍 PLL(または複数)を持ち、コントローラ自身とメモリ両方の全タイミングの元となる。例えば、メモリから戻ってくるリードストローブ(図 1 の下部に示す)は、PHY のオリジナルクロックから直接派生した信号である。

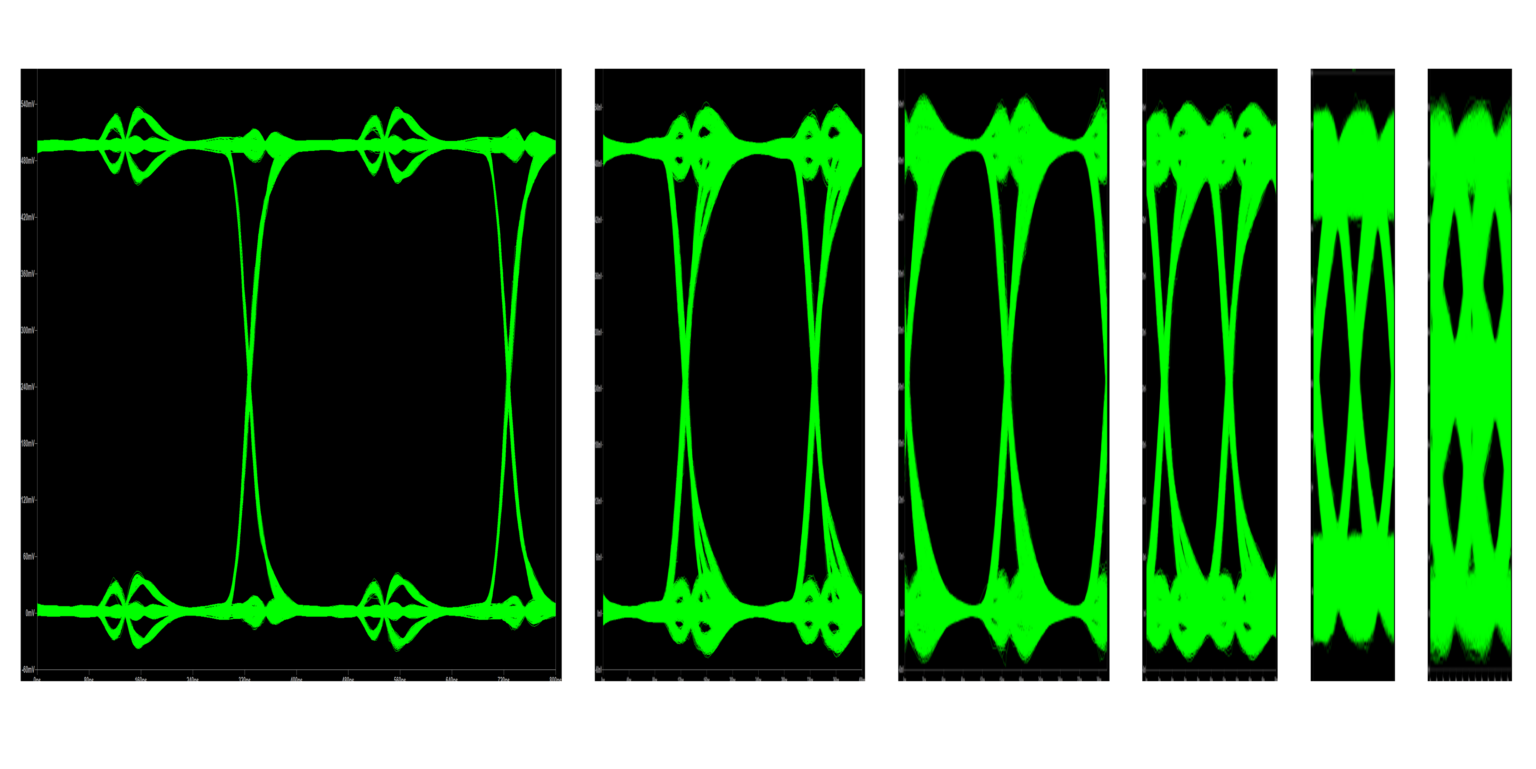

以上から、メモリ PHY の特性評価には複数の課題があることがわかる。しかし、その前に、メモリ PHY の転送速度の経時変化を図 2 に示す。この図では、メモリ PHY が最大速度で動作している典型的なアイダイアグラムを示している。理想的な条件(図 2 のような)でさえ、現世代のメモリ PHY をテストするパラダイムが、旧世代といかに異なるか を説明するのに、多くの言葉を必要としない!

図 1 と図 2 を参照すると、メモリ PHY の設計と検証の課題は以下の通りである:

- 完全パラレル送信バス(CAバスやDQバスなど)における真のビット誤り率の測定

- 完全並列送信バスにおけるクロストークとイコライゼーションの特性評価

- アットスピード・コマンド・デコードとエラー訂正の実行

- DQバスでの完全パラレル・レシーバ・ストレス・テストの実行

- コマンド間隔、メモリペイロード、トレーニング条件など、システムレベルの現象を理解する

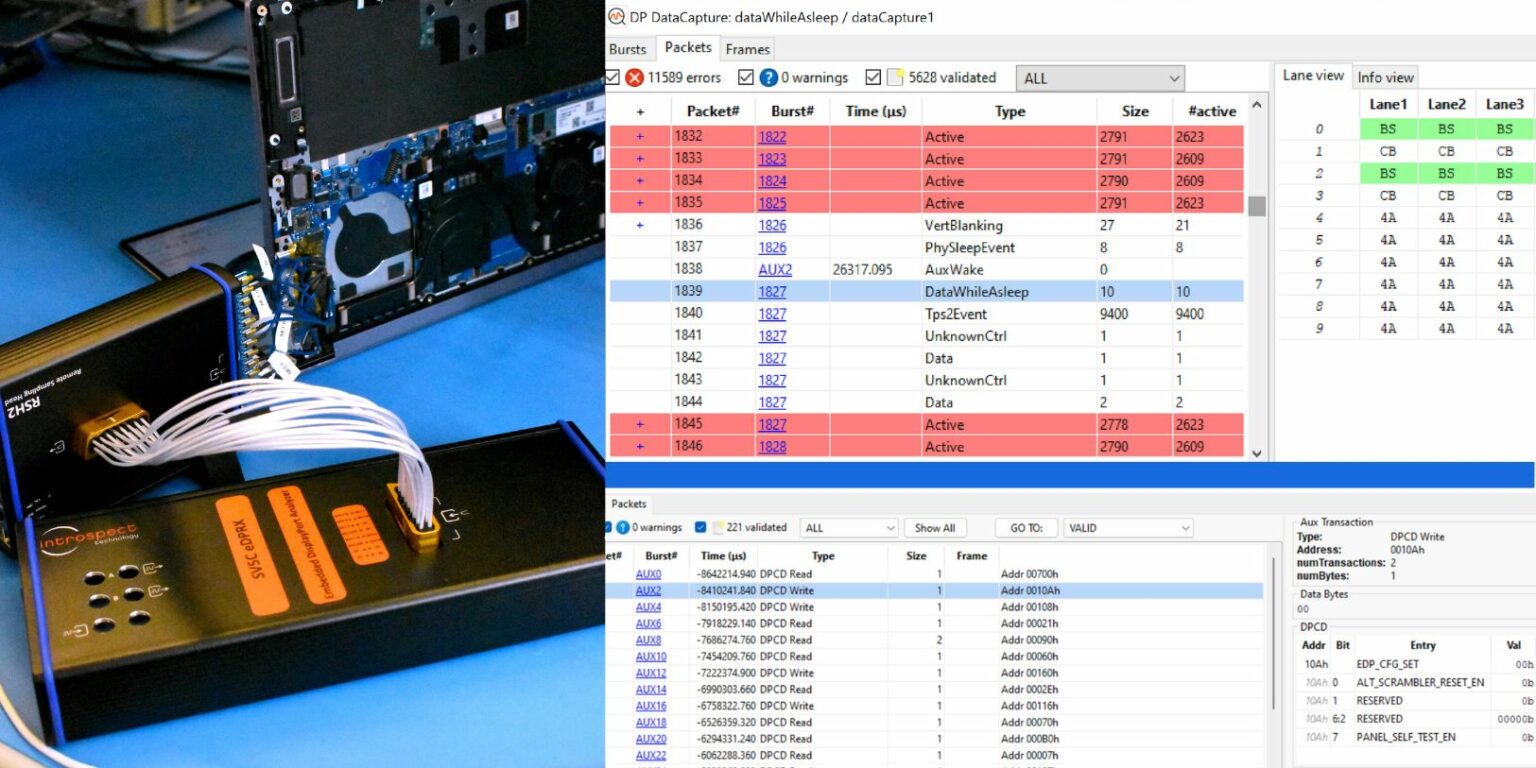

Introspect TechnologyのATE-on-Benchソリューションが可能にするテストセットアップ

CAバス・セットアップ

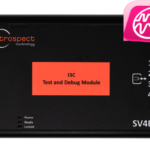

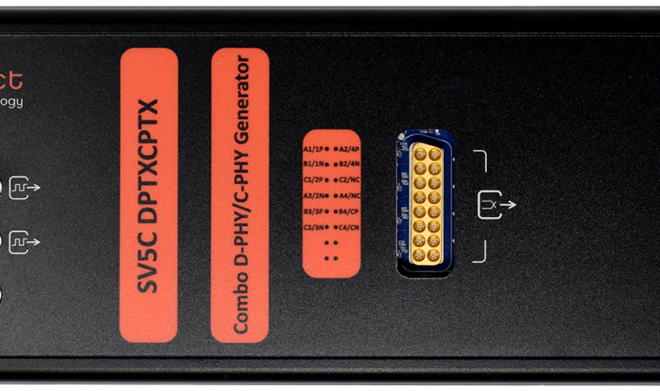

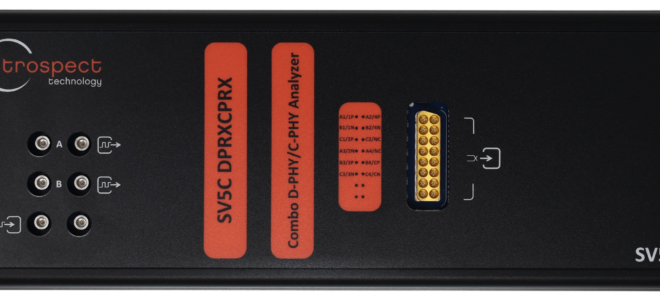

MR-DIMM に関するこのブログ記事など、以前のブログ記事で述べたように、Introspect は、メモリ・インターフェイスの特性評価と設計検証のための、一連の高度に洗練されたソリューショ ンを開発した。図 3 は、メモリ PHY 自体のコンテキストで、Introspect TechnologySV7C-17テストシステムを使用した CA バスのテスト方法を示しています。

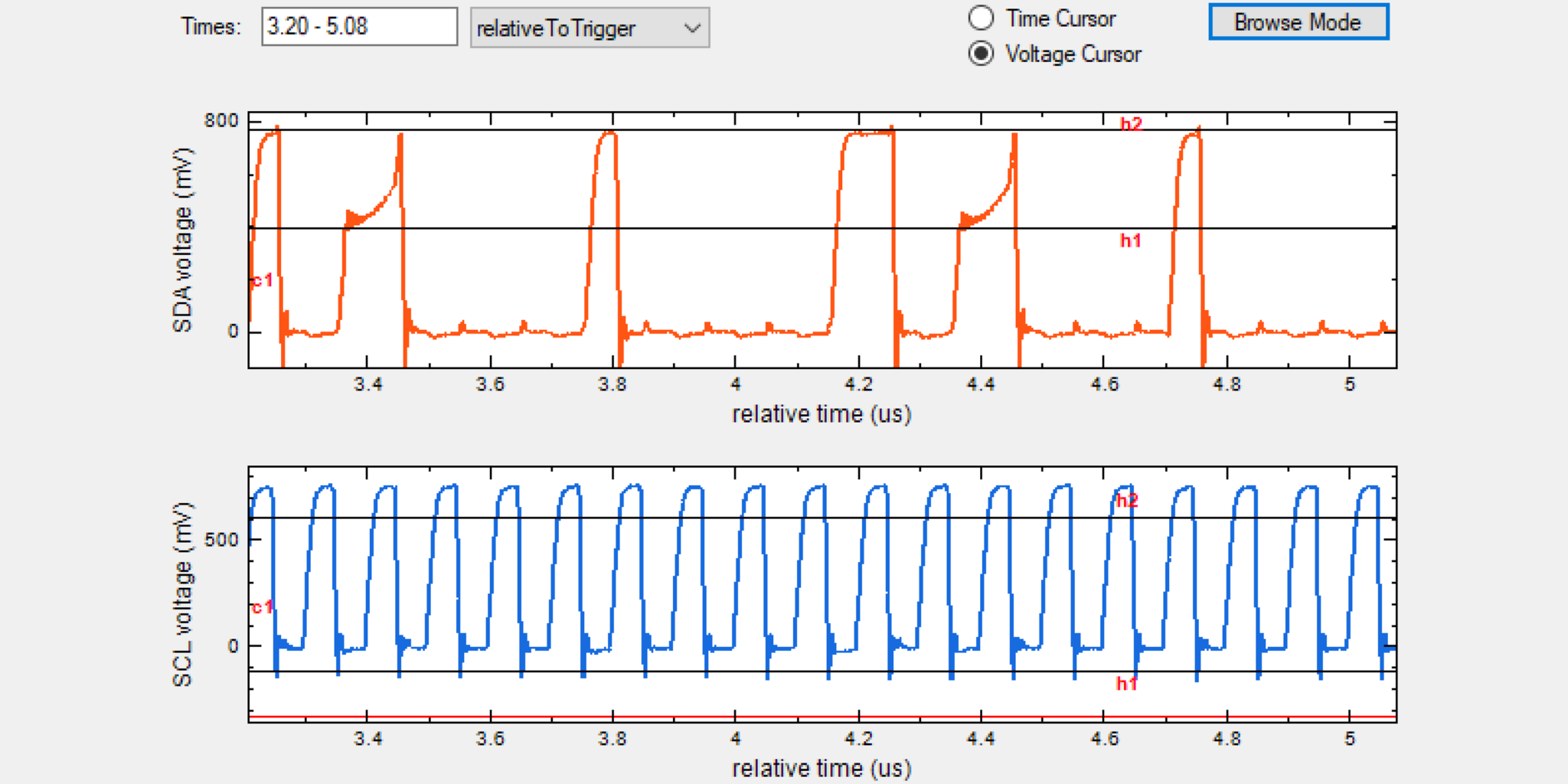

見てわかるように、SV7C は、あらゆる DDR、LPDDR、GDDR メモリ PHY の CA バス全体に接続するのに十分なピンを持っている!さらに、SV7C のレシーバピンは全て位相整合されており、これにより、スキューのオンザフライ自動測定と、メモリ PHY から送信されるコマンドのオンザフライデコードが可能である。図 4 と図 5 にそれぞれの測定例を示す。

DQバス・セットアップ

DQバスに移ると、このバスは双方向であるため、さらに面白くなります。つまり、レシーバー・テストが必要であり、ここでもSV7C-17やSV7C-PAM3のようなIntrospectツールが役に立ちます。図6を参照すると、1個のSV7C-17でDQバス全体にインターフェイスできます。そうすることで、SV7C-17 はメモリ PHY 内のレシーバで真のパラレルテストを行うことができる。

SV7Cのパターン処理能力は、任意の読み取りバーストデータの生成を可能にし、同様に重要なことは、バースト伝送内の任意の位置に障害を挿入できることである。これを図7に示す。

最後に、図 8 は、メモリ PHY レシーバのテストから直接得られたレシーバのバスタブカーブの例である。この図では、ストローブ信号にジッタ注入がない場合と、ジッタ注入が挿入されている場合の 2 つの条件下でのレシーバの性能を示している。

概要

現世代のメモリ・コントローラおよびメモリ PHY 設計は、メモリ市場においてかつてないレベルの性能を発揮することが期待されている。しかし、業界では、特性評価と設計の検証はほとんどアドホックなアプローチで行われてきました。Introspect Technologyのツールを使用することで、メモリPHYやメモリコントローラ集積回路の開発者は、チップの性能に関する深い洞察を得ることができ、これは最終的に、システム統合やメモリデバイスとの相互運用性でより高い成功率を達成するのに役立ちます。