GPUやCPUデバイスのコア数が急速に増加する中、これらのコアにデータを供給する、より多くのメモリをサポートする必要性がますます高まっています。しかし、現在の技術状況では、メモリ密度はコア数と同じペースで増加しておらず、これはサーバー・メーカーにとって大きな設計上の課題となっています。各CPUソケットにメモリ・チャネルを追加するだけでは、メモリ・バスが増えすぎ、サーバーのプリント基板アーキテクチャが非常に煩雑になります。このため、業界は次世代 DDR5 モジュール・アーキテクチャに取り組んでおり、その 1 つが MR-DIMM モジュールです。

MR-DIMMはMulti-Ranked Buffered Dual In-Line Memory Moduleの略で、このエキサイティングな新技術に取り組んでいる数え切れないほどのエンジニアから、親しみを込めてDIMM氏と呼ばれることもあります。この名前からもわかるように、MR-DIMMソリューションは、サーバーボード上のメモリモジュールのスロット数を増やすことなく、より多くのメモリと帯域幅を提供します。この設計のいくつかの重要な側面と、テストおよび測定への影響についてお読みください。

DRAMではなくCPUへの帯域幅を倍増

一言で言えば、MR-DIMM アーキテクチャは、CPU が単一の DIMM 上で 2 ランクのメモリに同時にアクセスできるようにするものです。この方法の利点は、DRAM デバイス自体がより高速なクロック周波数で動作することを期待されないことです。しかし、2 つの DRAM デバイスに同時にアクセスすることで、CPU は、DIMM から供給されるメモリ帯域幅を効果的に 2 倍にすることができます!

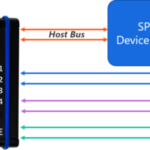

この一見単純なソリューションの鍵は2つあります。第一に、メモリコントローラと登録クロックドライバが、より高いクロック周波数をサポートできなければなりません。第二に、DIMMには、異なるDRAMデバイス間のデータの多重化を可能にする追加コンポーネントがモジュール上に含まれていなければなりません。

データバッファのカムバック

以前の世代の DDR メモリアーキテクチャでは、一部の DIMM モジュールは、モジュールのエッジコネクタと、モジュール内に収容された DRAM コンポーネントとの間にデータバッファを含んでいました。しかし、DDR5 R-DIMM モジュールの最近の実装では、そのようなデータバッファは必要ありませんでした。現在では、MR-DIMM テクノロジーがこの状況を変え、データバッファが復活しただけでなく、DIMM 自体の動作原理の中心にもなっています。MDBと呼ばれるこの新種のデータバッファは、非常に洗練されている。前例のないクロック周波数での信号コンディショニングを可能にし、メモリデバイス間でインテリジェントにデータを多重化できる高度なプログラマビリティも備えている。

テストの意味

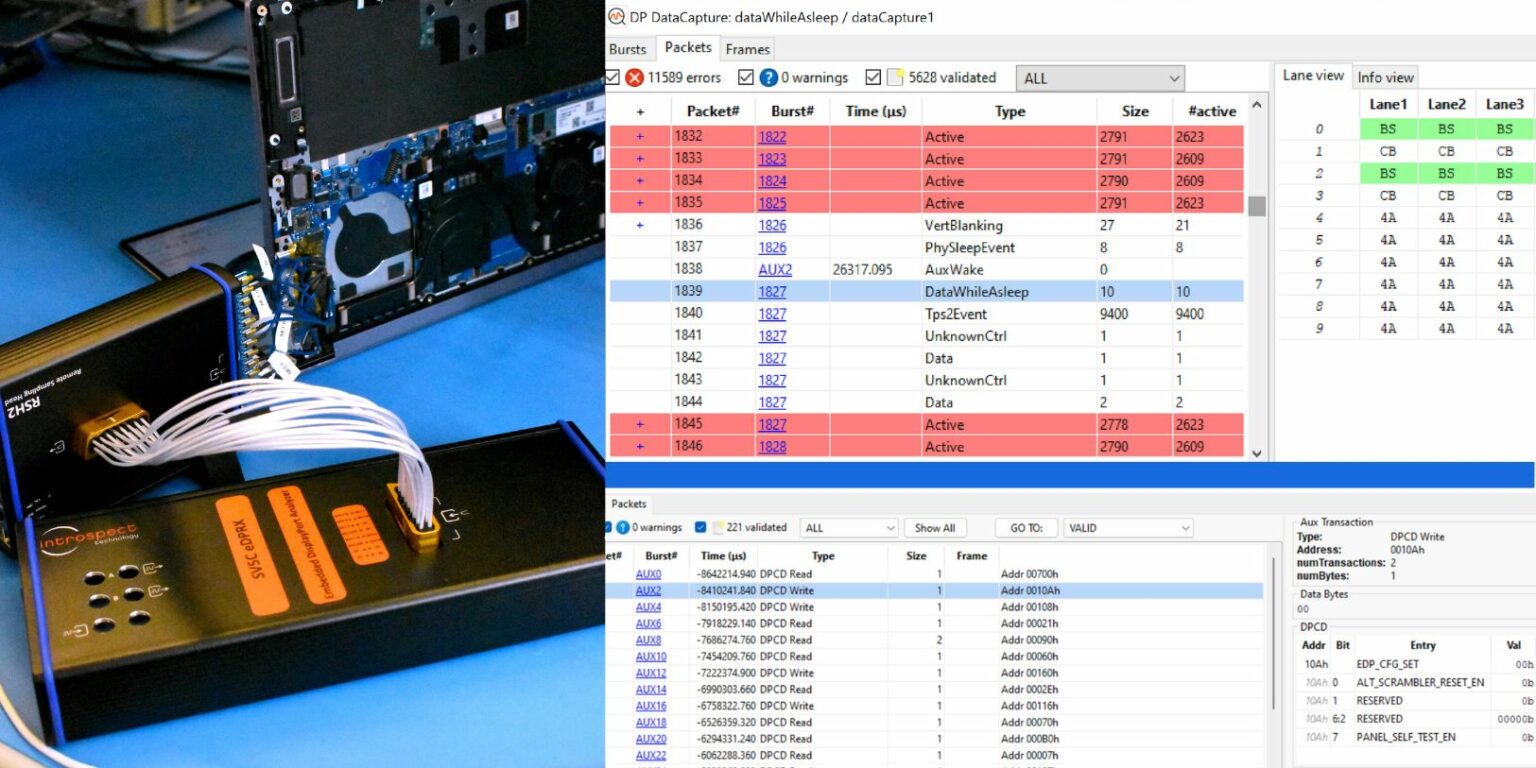

MR-DIMMモジュールとそのモジュールを構成するデバイスを真にテストするには、まったく新しいカテゴリーのテストおよび測定機器が必要です。Introspect Technologyは、このような種類の測定器を開発できるよう、10年以上かけて技術を磨いてきました。以下のセクションでは、このカテゴリーの3つの特徴について説明します。

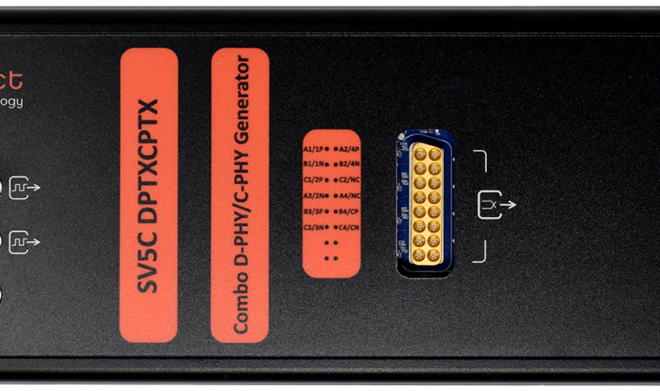

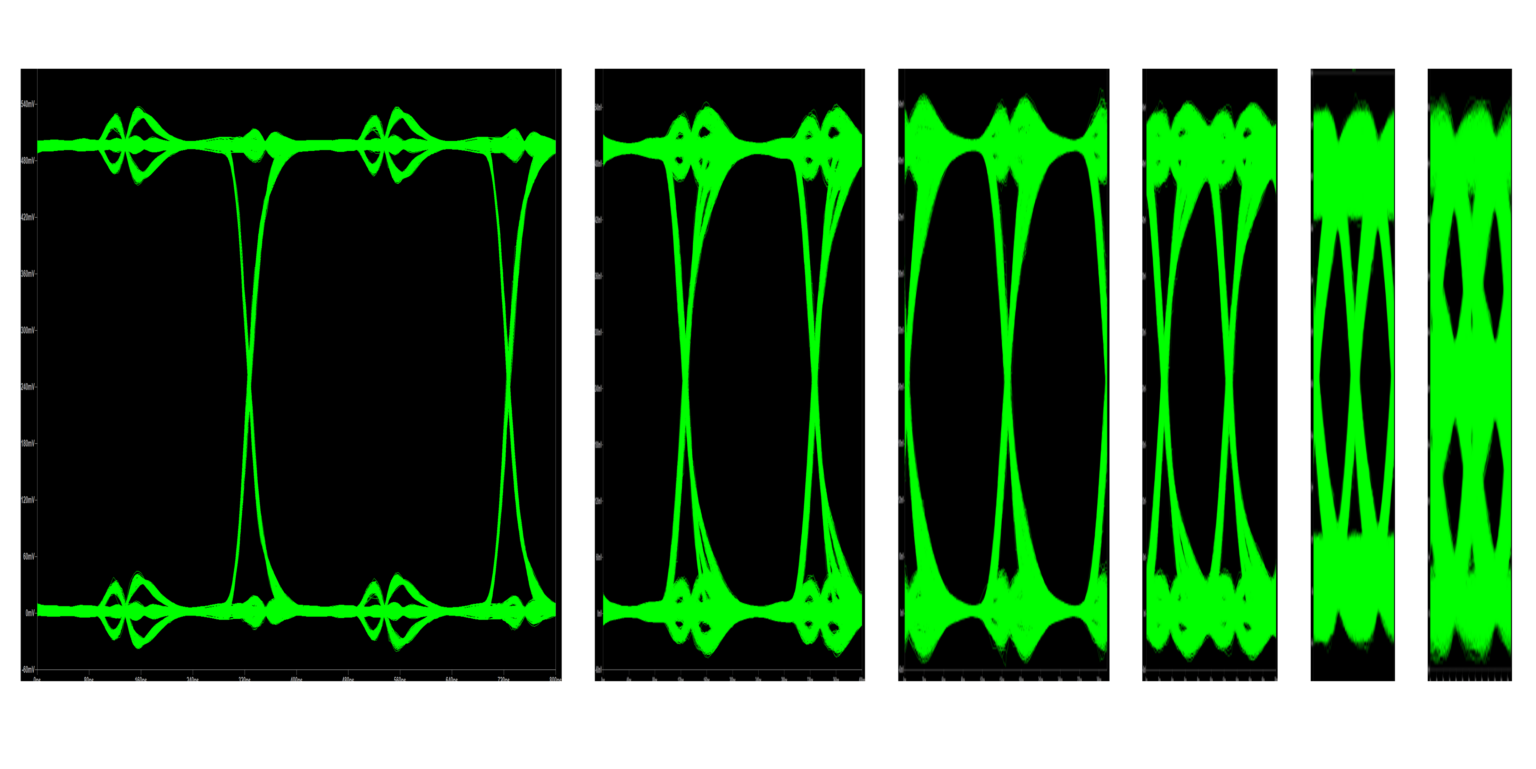

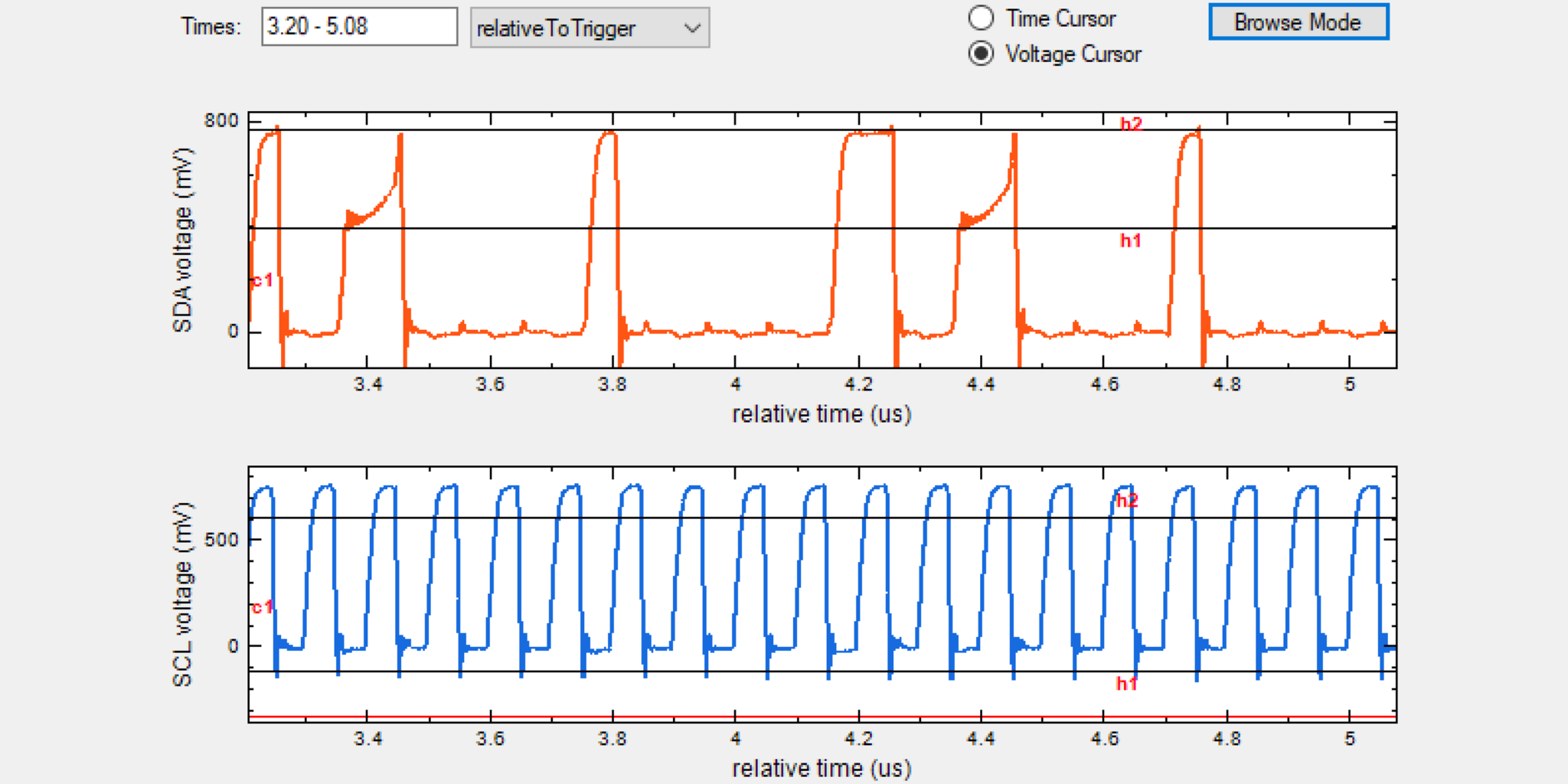

超高速、位相整合パターンジェネレーター

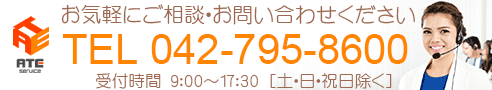

MR-DIMM技術は、17Gbpsを超える速度で動作する非常に広いデジタルバスを作り出すという点で、実に野心的である。このようなチャネル数とデータ・レートでデジタル・レシーバをテストするのは、難しい注文です。必要なのは、数十チャンネルをサポートできるパターン・ジェネレーターであり、各チャンネルは非常に高速で動作し、各チャンネルを接続するために使用されるテスト・ケーブル(ワイヤ)の位相整合をしばしば超える位相整合の要件を持ちます。図1はこの概念を示している。

図1:多数の位相整合パターンジェネレーターの必要性。

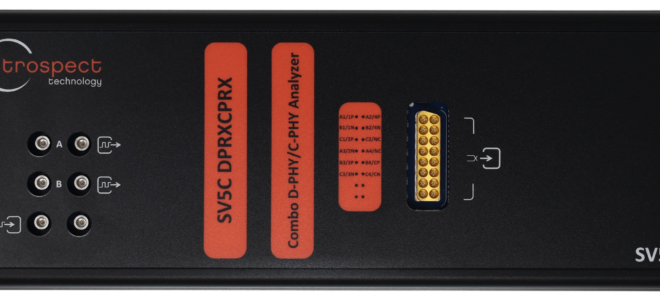

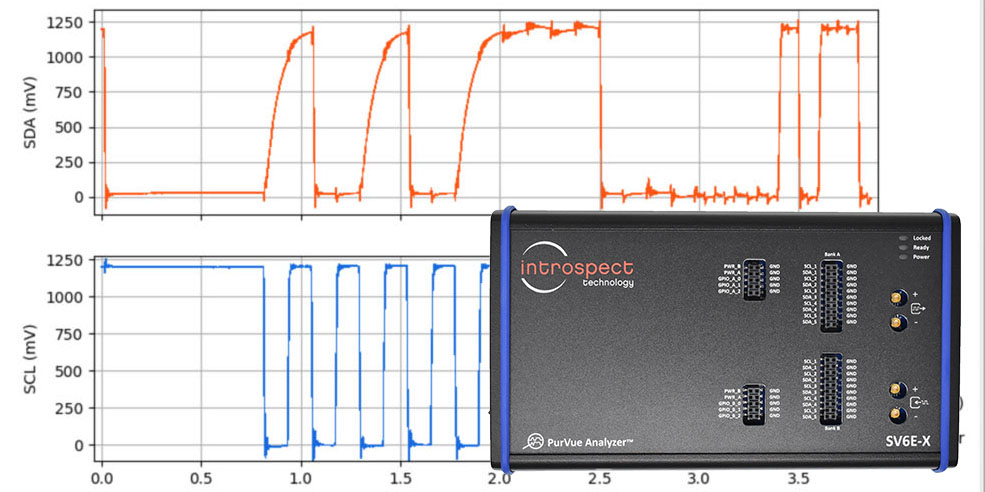

超高速クロックフォワード・パターン・エラー検出器

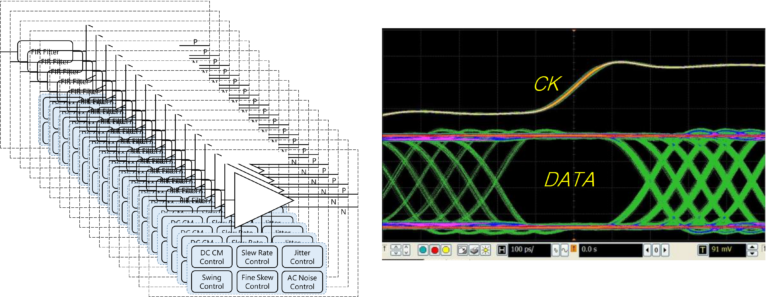

同様に、デバイス・トランスミッターからのデータを検証し、そのアナログ性能を特徴付けるには、多数のチャンネルが必要です。これは業界の大きなハードルであり、Introspect Technologyがテストおよび測定装置で正面から取り組んだ課題です。図2はこの概念を示しています。

図2:位相整合された多数の順方向クロック・エラー検出器が必要である。

リアルタイムプロトコル対応ハンドシェイク

上記では、MR-DIMMとそれを搭載したサーバーの設計の精巧さについて少し触れました。このような高度な設計は、非常に詳細なプロトコルによって支配されており、これらのプロトコルはテスト中に行使されなければなりません。

Introspectテクノロジーソリューション

SV7C-17は、DDR5およびGDDR6などのメモリ・インターフェース技術に特化して開発された、カテゴリーを創造するATE-on-Benchテスト測定装置です。17Gbpsを超えるデータレートでDDR5バス全体を動作させながら、バス上でパラメトリック測定とトレーニング測定を行うことができる世界で唯一の測定器です。また、IntrospectのPythonベースの統合開発環境であるPinetreeを搭載しています。SV7C-17を使用することで、エンジニアは、MRCDやMDBデバイスに見られるようなメモリコントローラーインターフェースやコンポーネントインターフェース、さらにはMR-DIMMモジュール全体をテストし、検証することができます。