PCI Express (PCIe) リンクの物理層を検証する最速の方法

PCI Expressは世界で最も古いSerDes規格の1つであり、ラップトップ、パーソナル・コンピュータ、サーバ、さらには旧来のメインフレーム・コンピュータのコンピュータ・アーキテクチャの進歩に貢献してきました。コンピュータ」産業の真の雄であるPCI Expressは、過去数十年の間に劇的に進化し、現在では揮発性メモリや不揮発性メモリなどの魅力的なアプリケーションで利用され続けています。Introspect Technologyは、PCI Expressのエンドポイントにおける物理層のマージン検証要件にどのように対応しているか、ご覧ください。IPメーカー、チップメーカー、モジュールメーカー、システムメーカーを問わず、送信機と受信機が適切に構築、接続されているかどうかを迅速に検証することに大きな喜びを見出すことができるでしょう。

ハードウェアのセットアップ

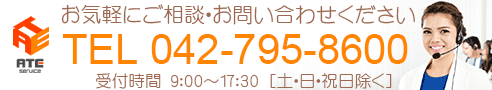

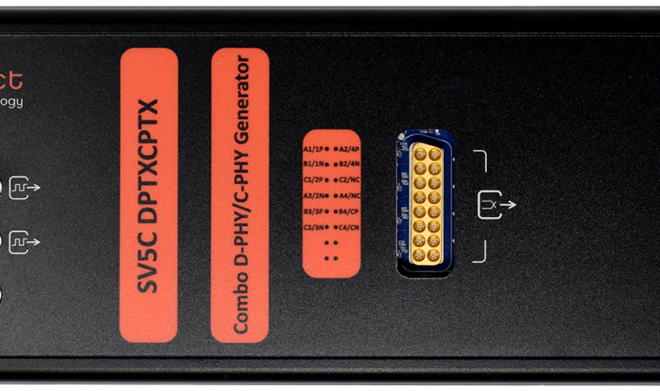

PCI Expressのテストには、さまざまなIntrospect Technology製品を使用することができます。例えば、下図はSV1C-12システムです。これは8レーンの12.5Gbpsシステムで、Gen3テストに最適です。また、SV7C-17はx16 Gen4テストに、SV2C-32はx8 Gen5テストに理想的です。そういえば、SV2C-PAM4はGen6で64GbpsのBERテストができるって言ってたっけ?

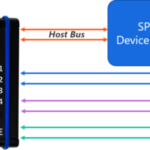

図1のハードウェア設定は、Introspectツールが非常に魅力的である理由の1つです。右側には、基準クロック注入ソース、パターンジェネレータ、パターンレシーバを持つ単一の「BERT」システムがあります。さらに、デバイスのリセット信号などを制御するための補助IO信号も備えています。このオールインワン・アーキテクチャにより、PCI Expressリンクのトランスミッタおよびレシーバのマージンを検証する問題は、ハードウェアの問題ではなく、ソフトウェアまたは自動化の問題になります。

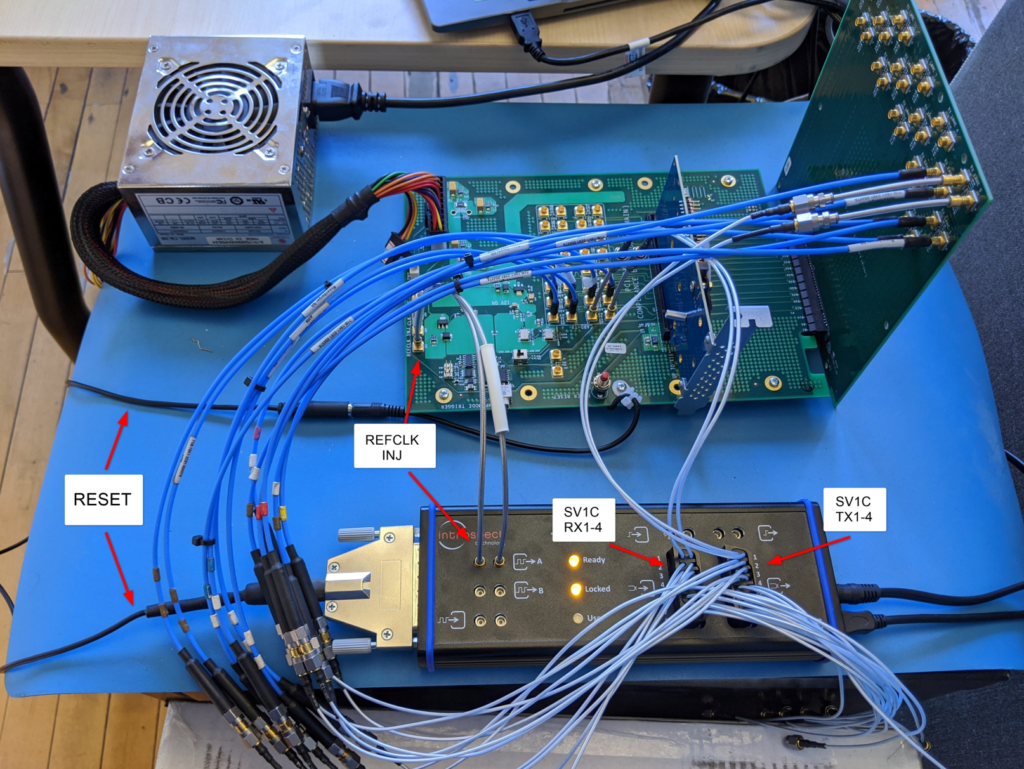

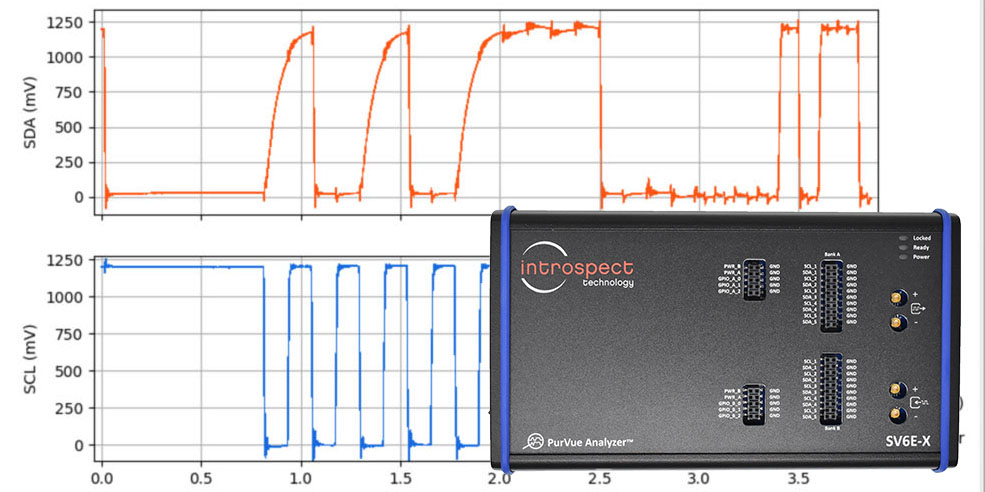

次の図は、コンプライアンス・ベース・ボードで一般的にどのように電源が接続されているかを示し、その次の図は、どのようにリセット信号を追加できるかを示している。

ソフトウェアのセットアップ

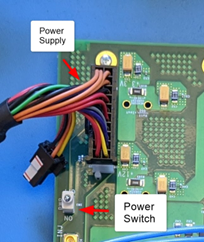

前述のとおり、ソフトウェアの自動化は、PCI Express リンクの検証に Introspect ツールを使用するもう一つの大きな利点です。これらのツールはすべて、Pythonベースの自動化環境である、受賞歴のあるIntrospect ESPソフトウェア上で動作します。Pythonフレームワーク内で、テストしたいデータレートを選択することができ、PCIeレートが何であるかをカスタマイズすることも可能です。例えば、次の図は、Gen3データレートを正確に8Gbpsに設定することを示しています。

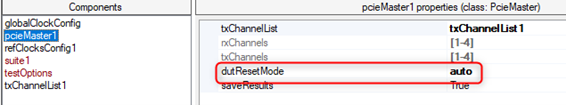

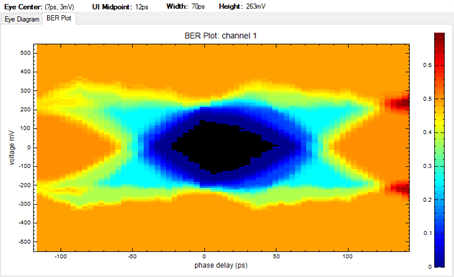

同様に、図5は、ソフトウェア内のPythonコンポーネントクラスの属性を使用して、さまざまなテストオプションを設定できることを示しています。ここでは、DUT の自動リセットを選択しています。つまり、上記の図 3 のハードウェアリセット接続を利用 していることになります。

Introspect ESPソフトウェアには、PCI Expressトランスミッタのシグナルインテグリティ試験とレシーバの感度試験のための機能もあらかじめ組み込まれています。たとえば、図6は、実行するさまざまなテストのオプションを提供するユーザーインターフェイスです。gen3SjTolTestのようなテストでTrueを選択するだけで、ツールは自動的にPCI Expressエンドポイントをトレーニングし、それに対してジッタ耐性のテストを実行することができます。

結果のサンプル

以下のセクションでは、Introspect PCI Expressツールによって生成されるテスト・レポートの簡単な例をいくつか示しま す。まず、リンクがアップしていることを確認するための基本的なパターン・チェックを示します。次に、実際のデバイス性能の特性評価を示します。

Gen 1コンプライアンス・パターン・チェック

電源投入時、PCI Express準拠のデバイスは、レシーバの負荷インピーダンスを検出することでアクティブレーンを特定し、それらのレーン上でTS1オーダセットの送信を開始します。もしデバイスがレーン検出から24ms以内に少なくとも8つの連続したトレーニングシーケンスを受信しない場合、デバイスはすべてのアクティブレーンでコンプライアンスパターンの送信を開始します。このテストでは、送信されたコンプライアンスパターンを検出することによって、DUTがGen1レート(2.5Gbps)で動作可能かどうか、どのレーンが応答するトランスミッターとレシーバーを持っているかを判断しています。

Starting 'testCase_gen1ComplianceCheck' TestCase: Gen 1 Compliance Pattern Check Starting Compliance Pattern Check Pattern detection successful on channels [1, 2, 3, 4] Length of detected compliance pattern (in 10 bit symbols): [64, 64, 64, 64] Number of loops locked: [3405807, 3405806, 3405807, 3405907] Finished 'testCase_gen1ComplianceCheck'

Gen1 修正コンプライアンスパターンチェック

アクティブレーンを特定した後、PCI Express デバイスは TS1 オーダーセットの送信を開始し、他のデバイスからの TS1 オーダーセットの受信を監視します。少なくとも 8 つの TS1 を受信すると、デバイスは広告されたデータレート識別子と Compliance Receive ビットを検査します。Compliance Receiveビットがアサートされた場合、デバイスは自身と受信したTS1の両方がサポートする最大レートに移行し、Modified Compliance Patternの送信と監視を開始する。送信されたパターンのエラーステータスの内容は、デバイスが受信したModified Compliance Patternを正常に検出したかどうかによって決定される。以下のログでは、DUTがGen1レート(2.5Gbps)で動作し、すべてのアクティブレーンでModified Complianceパターンを正常に受信できるかを判断しています。

Starting 'testCase_gen1ModComplianceCheck' TestCase: Gen 1 Modified Compliance Pattern Check Starting TX ChannelList setup txChannelList1: Channels 1-4 are linked due to the PatGenController for PatternTimelines Starting Modified Compliance Pattern Check Pattern detection successful on channels [1, 2, 3, 4] Error Status Bytes: [0, 0, 0, 0] Length of detected compliance pattern (in 10 bit symbols): [128, 128, 128, 128] Number of loops locked: [13, 123, 3123204, 3119793] Training Sequence Symbols 1-15: Channel 1: F7 F7 FF 1E 00 00 4A 4A 4A 4A 4A 4A 4A 4A 4A Channel 2: F7 F7 FF 1E 00 00 4A 4A 4A 4A 4A 4A 4A 4A 4A Channel 3: F7 F7 FF 1E 00 00 4A 4A 4A 4A 4A 4A 4A 4A 4A Channel 4: F7 F7 FF 1E 00 00 4A 4A 4A 4A 4A 4A 4A 4A 4A Finished 'testCase_gen1ModComplianceCheck'

トランスミッター高速シグナルインテグリティテスト

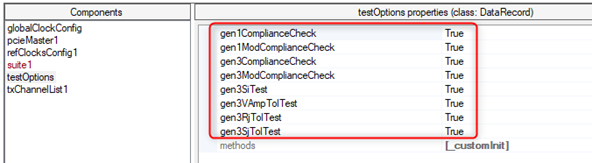

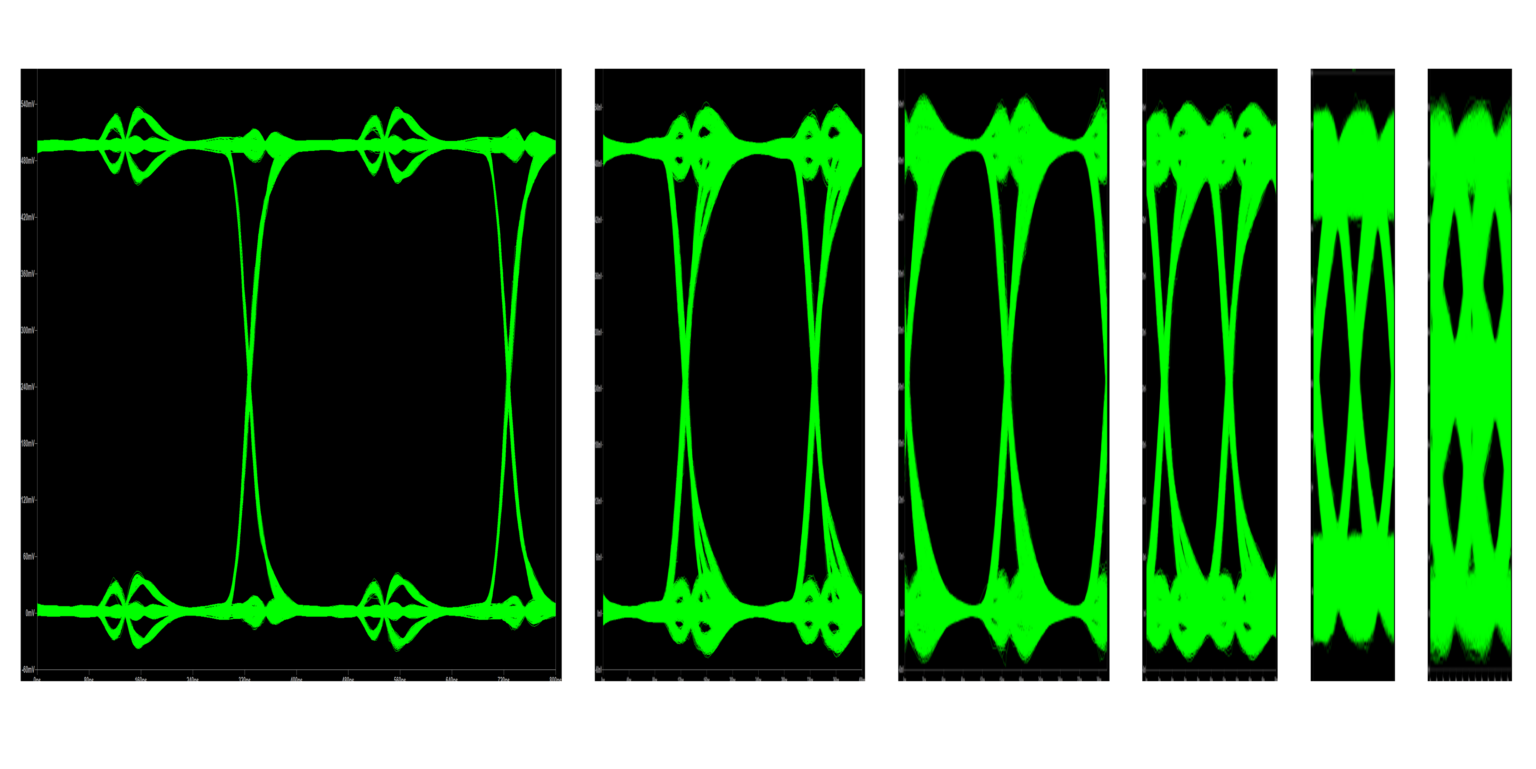

アクティブレーンを識別し、TS1オーダーセットを受信できなかった後、より高度なシグナルインテグリティテストに進みます。たとえば、すべてのトランスミッタープリセットは、Introspectツールに組み込まれている適切な自動化手順によってテストされます。次のグラフは、4つのアクティブレーンでのトランスミッターバスタブプロットを示しています。このバスタブプロットは、すべてのレーンで同時に取得されました。

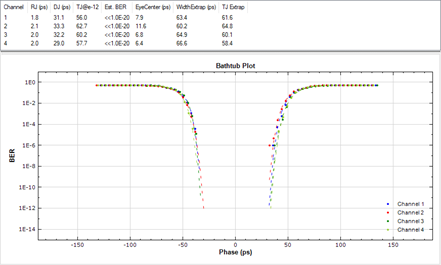

同様に、フルアイ・ダイアグラムのテストも得られ、その一例を図8に示します。これらのアイダイアグラムは、真のBERベースのアイダイアグラムであり、統計的に深い測定値を表していることを意味します。例えば、以下に示すアイダイアグラムは、1e-6エラー確率の設定でキャプチャされたものです。

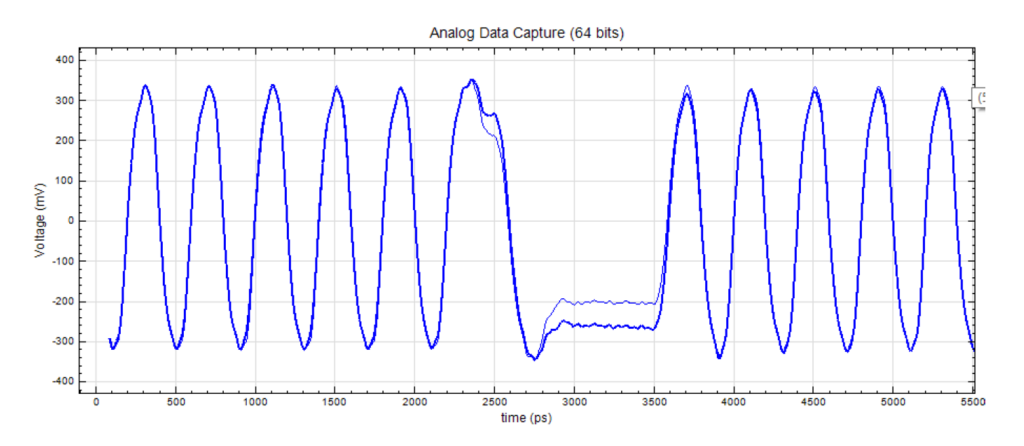

最後に、オーバーシュートなどのプリセット測定は、アナログキャプチャツールを用いて行うことができます。図9では、アナログキャプチャツールでオシロスコープ波形を平均化し、それを解析して電圧振幅やオーバーシュートなどの測定値を抽出した結果を示しています。

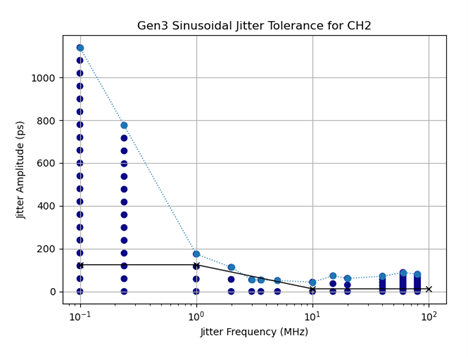

レシーバのジッタ耐性の例

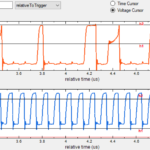

次に、さまざまなアナログ特性に対するDUTの耐性を測定するために使用されるIntrospectツールの障害能力について見ていきます。図10は、ソフトウェアのPCI Expressツールを使用して自動的に構築されたジッタ耐性のグラフです。PCI Expressリンクの各チャンネルに対して個別のプロットが生成され、これらの測定値が同時に得られることに注意してください。

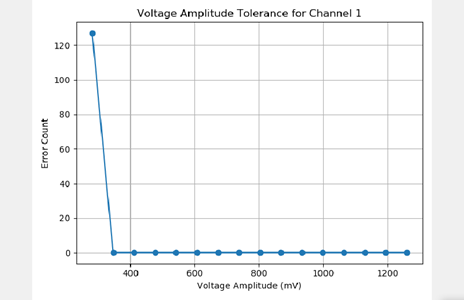

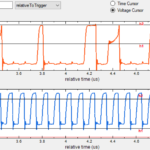

最後に、次の図は、実際のPCI Expressレシーバーでのレシーバー電圧感度テストを示しています。グラフは、プログラムされた電圧振幅の関数として、レシーバのエラーカウントを示します。

まとめ

この記事では、Introspect Technology Cシリーズ個人用SerDesテスターを使用して、PCI Expressリンクのシグナルインテグリティを迅速に検証する方法について説明しました。これは、システム・レベルでのランダムで断続的な動作のデバッグにかかる日数を短縮できるため、重要なことです。シグナル・インテグリティが確実であることが分かっていれば、ステート・マシンの不安定性やソフトウェアのバグなど、他の間欠性の原因に集中することができます。