JEDECアライアンスは、最新のグラフィックス・メモリ仕様であるグラフィックス・ダブル・データ・レート7 SGRAM規格(GDDR7)-JESD239-を発表しました。この新しい規格には、いくつかの重大な技術革新と進歩が導入されているため、私たちはこれ以上ないほど興奮しています。このような進歩は当然、一見克服不可能なテスト課題を生み出しますが、これこそがIntrospect Technologyの存在理由です。私たちは、業界がより大きな技術的ハードルに対処できるよう支援します。

GDDR7によって、より高速で大容量のメモリが実現されることが期待されているが、本稿では、この規格の技術的側面のいくつかに焦点を当てる。これは、この規格を支えるエンジニアと、これまでグラフィックス・メモリ・インターフェース技術を進歩させるために費やされてきた数十年にわたる研究に敬意を表するものである。それではどうぞ。エンジニアだけが理解できるGDDR7とGDDR6の違いトップ3です!

1.PAM3信号とボーレートに対する高いビットレート

デジタル回路が存在する限り、コンピューター・アーキテクチャはデータのバイナリ表現に依存してきた。私たちが開くファイル、見るビデオ、プレイするゲームはすべて、コンピュータやスマートフォン内のコンポーネント間を流れる膨大な1と0の川によって最終的に構築される。技術用語では、これはパルス振幅変調(PAM)と呼ばれる符号化の一形態であり、長い間、データは2つのレベルのみで構成される非復帰ゼロ(NRZ)PAM信号方式を使用して電子回路上で伝送されてきた。

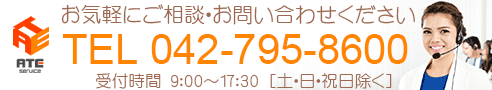

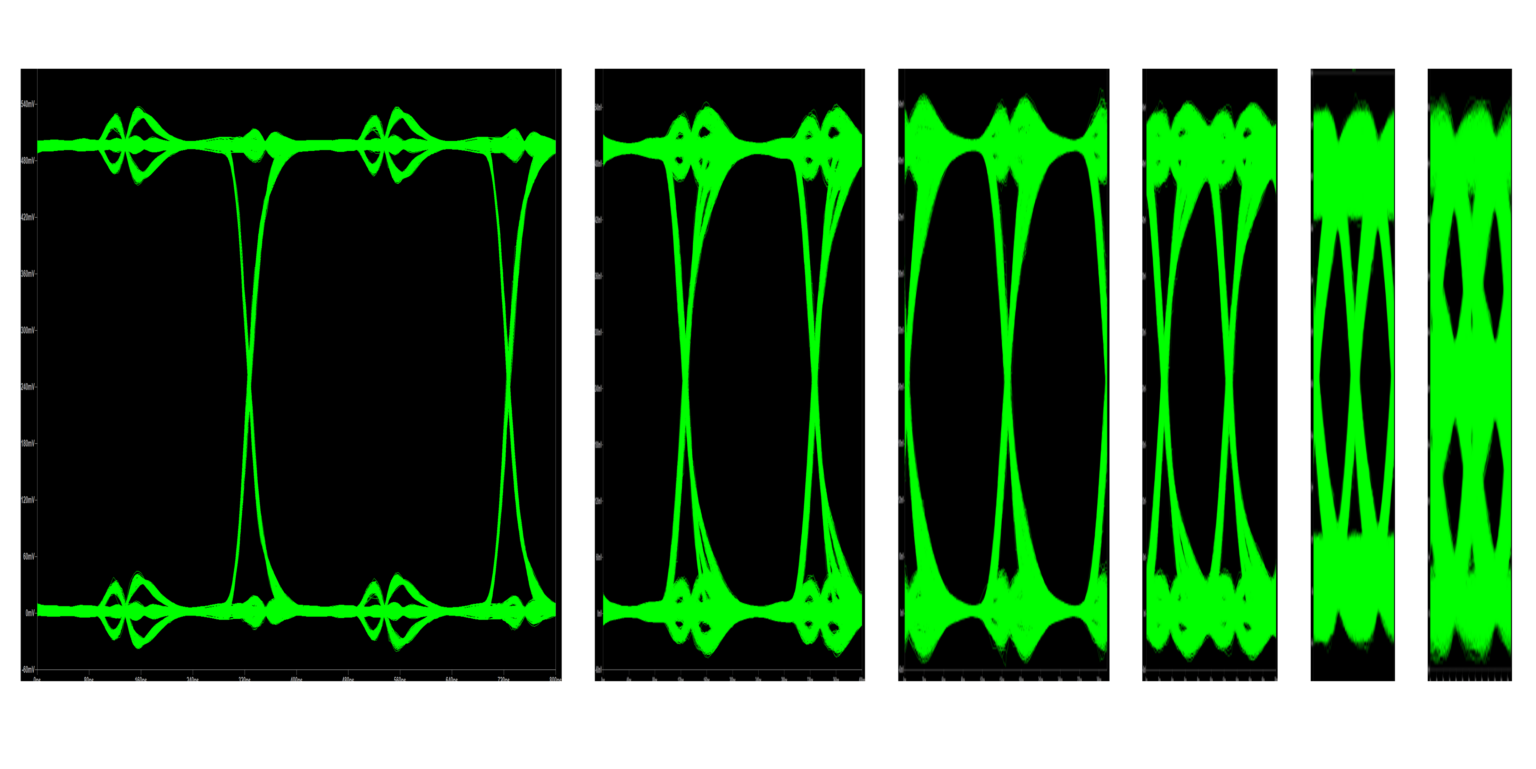

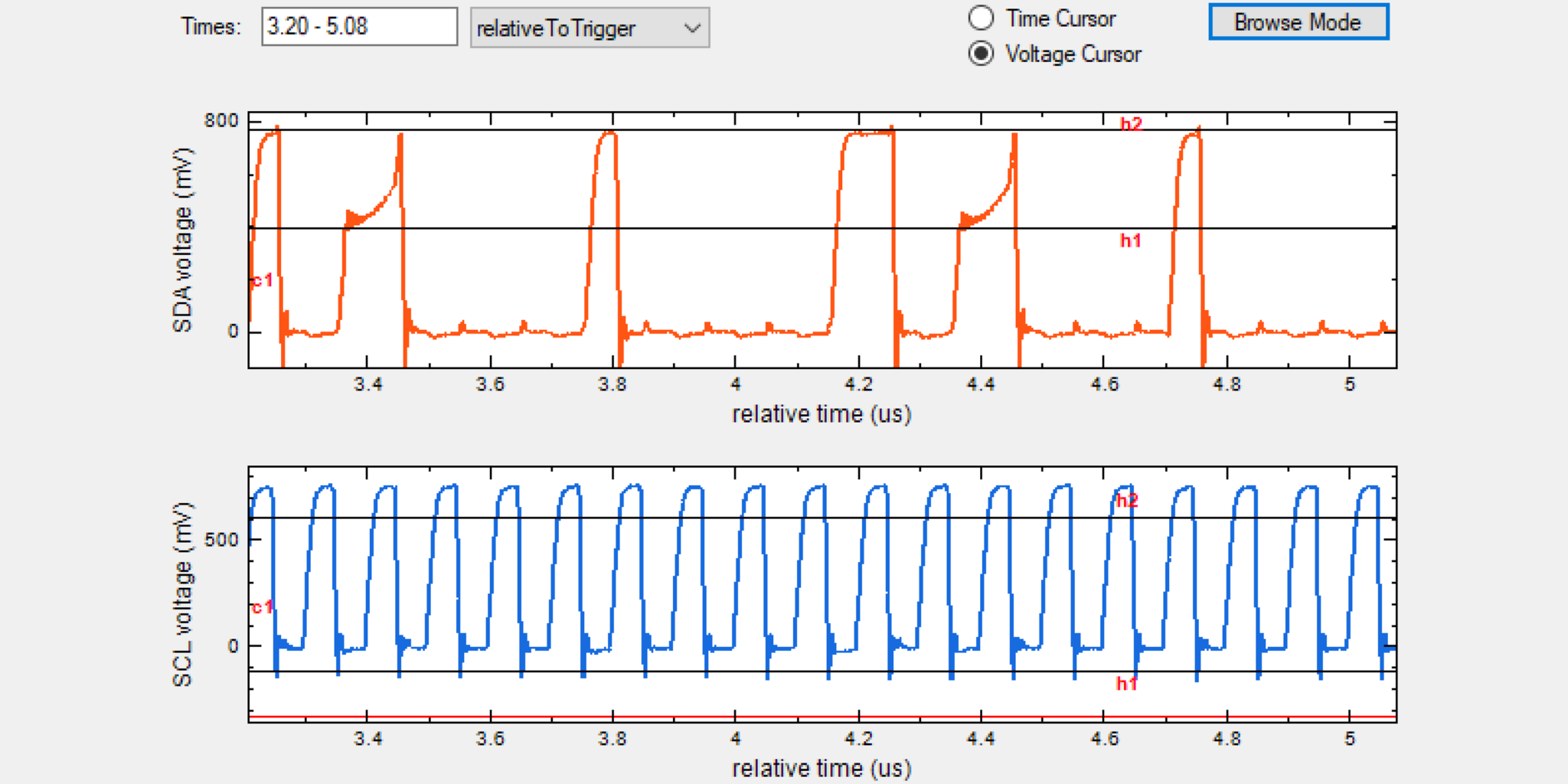

より高い帯域幅を可能にするため、GDDR7 は PAM3 と呼ばれる別の符号化方式に依存しており、これは以下の図に示されている。

図1に見られるように、これは別のパルス振幅変調方式で、データをエンコードするレベル数が2ではなく3になっている。つまり、各クロック期間は1ビットではなく2ビットのデータをエンコードすることになる。2より大きなPAM方式を採用する利点は、所定のクロックレートに対するスループットが向上することである。つまり、GDDR7メモリは、GDDR6メモリと同じ期間内に、より多くのデータを送信することができますが、より速いクロック速度で動作する必要はありません。

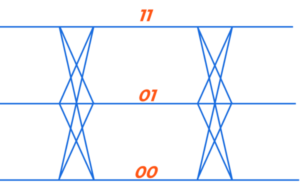

しかし、PAM3シグナリングだけがGDDR7の革新ではない。具体的には、あるクロック周期で 2 倍のデータを本当に伝送したいのであれば、PAM4 方式を使用することもできた。少なくともそのような方式では、下図に示すように、各電圧レベルは正確に2ビットをエンコードすることになる。

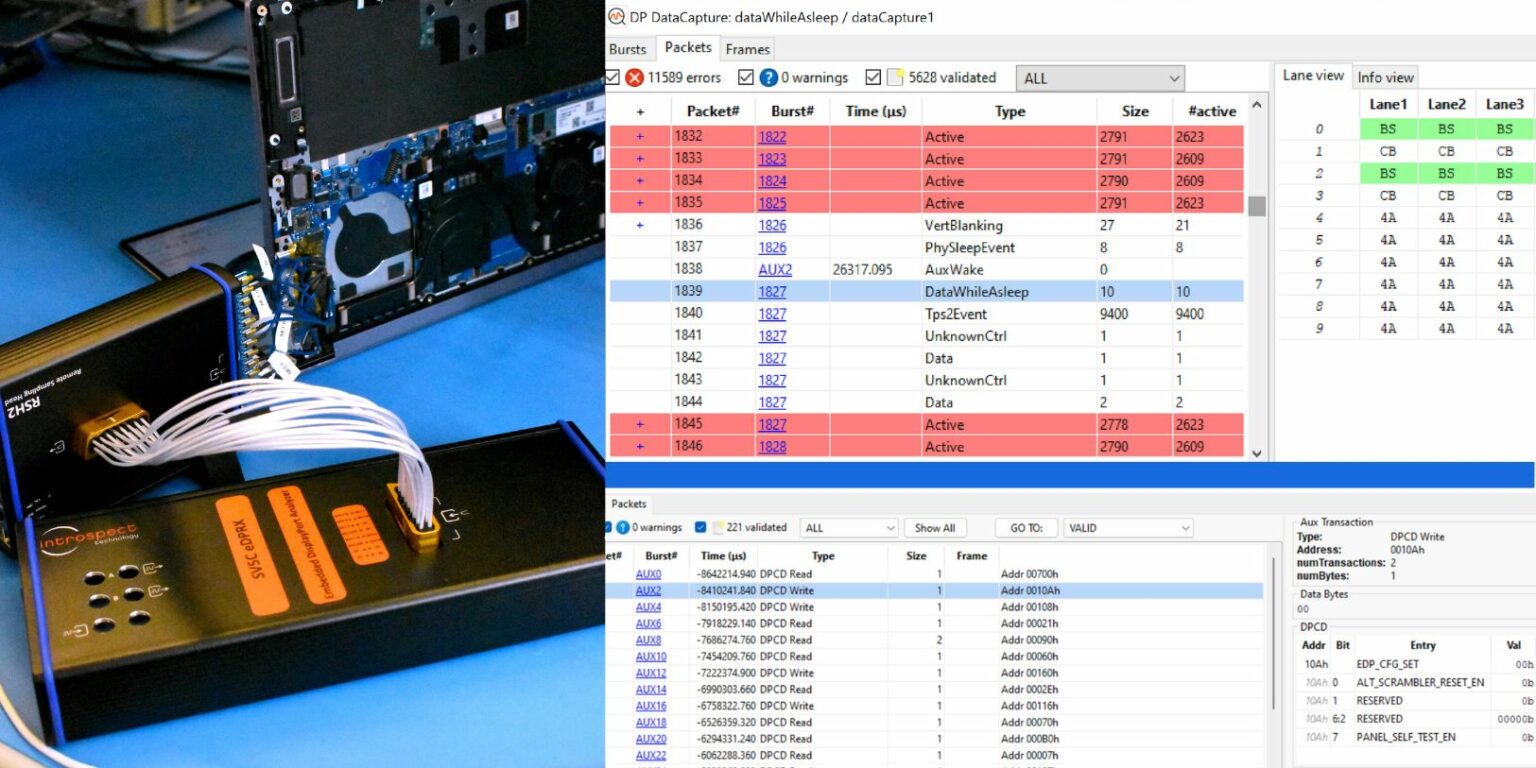

この図を見ただけで、電圧レベル間の遷移が多いことと、レベル間の電圧分離が小さいことの2つに気づく。これらの現象はいずれも、メモリとのデータ転送におけるビット・エラーのリスクを増大させる。そのため、GDDR7 は PAM3 エンコーディング方式のみに固執し、さらに、この規格では真の 2 倍の帯域幅改善を達成するために、巧妙な「バースト」設計と巧妙なシンボルエンコーディングを使用しています。これらのテクニックの一部は、ここでは説明できないほど高度なものです。しかし、当社のM5512 GDDR7メモリ・テスト・システムを使用すれば、これらの技術を実際に見ることができる。

2.コマンドバスとアドレスバスのピンが少ない

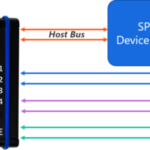

コマンド・アドレス(CA)バスは、グラフィックス・プロセッサ(GPU)とGDDRメモリ間のデジタル接続です。GPUはCAバスを介してメモリに読み取りコマンドと書き込みコマンドを送信し、データをフェッチしたりデータを保存したりするための座標(アドレス)も送信します。そのため、GDDRメモリの動作にとって非常に重要です。

GDDR6 から GDDR7 への移行に伴い、CA バスのピン数は劇的に減少した!これは、ほぼ同じパッケージ・サイズで、より多くの独立したメモリ・チャネルを統合できることを意味します。これにより、GDDR7メモリを使用する際の柔軟性がさらに高まります。

ハードウェアを設計する前に、必ずデバイスの正確なピンアウトを参照してください。しかし、おわかりのように、GDDR7 規格は、2 チャネルしかないメモリを 1 つのパッケージに 4 チャネル詰め込むことで、業界のさらなる小型化を可能にしています。

3.新しいリード/ライト・トレーニング・モード

最後に、DDR、LPDDR、および GDDR インターフェースでは、トレーニングはメモリを動作させるための重要なステップです。トレーニングなしでは、PCBトレース配線の制約や環境の変化(温度など)により、GPUやCPUがメモリから誤ったデータを取得することになります。GDDR7 では、JEDEC アライアンスは多くの新しい読み出しおよび書き込みトレーニング・アルゴリズムを導入しました。これらは、トレーニング・ステップをより効率的かつ迅速に行うためのものである。詳細については、JESD239 仕様をお読みください。

GDDR7がAIや次世代技術をどのように加速させるのか、私たちは期待しています。未来は無限であり、私たちはここにいて、すべてのステップをテストする準備ができています。